The 2025 IEEE 75th Electronic Components and Technology Conference May 27 – 30, 2025

# 2025 Advance Program

Gaylord Texan Resort & Convention Center Dallas, Texas, USA

Sponsored by

Years of Pushing the Scale of Connectivity

Program Supported by

For more information visit www.ECTC.net

## **INTRODUCTION FROM THE IEEE 75TH ECTC PROGRAM CHAIR PRZEMYSLAW GROMALA**

# The 2025 IEEE 75th Electronic Components and Technology Conference (ECTC) at the Gaylord Texan Resort & Convention Center, Dallas, Texas • May 27 - 30, 2025

On behalf of the Program and Executive Committees, I am delighted to invite you to the IEEE 75th Electronic Components and Technology Conference (ECTC). This premier event, sponsored by the IEEE Electronics Packaging Society, will take place May 27–30, 2025, at the Gaylord Texan Resort & Convention Center in Dallas, Texas. ECTC brings together over 2,000 professionals from across the global microelectronics packaging industry, including manufacturers, design houses, foundries, material suppliers, universities, and investors. Join us to connect with key stakeholders and explore cuttingedge advancements in the field.

The 75th ECTC conference will introduce several new and exciting program events. First, the number of special sessions on Tuesday has more than doubled – from four to nine – with two sessions running in parallel and some really exciting topics and panelists. To support workforce development, we are launching a new student engagement program. We have partnered with local universities and colleges to invite approximately 20 undergraduate students on Wednesday, introducing them to the fascinating world of microelectronics packaging and technologies. Additionally, this year features a student competition challenge. Three winning teams will be invited to the conference to present their projects during Pitch Night, co-organized with the Start-Up Competition Challenge. Lastly, our Thursday ECTC Reception Gala will be expanded with a special event to celebrate the conference's 75th anniversary.

At the 75th ECTC, approximately 400 technical papers will be presented in 36 oral sessions and five interactive sessions. Authors from over 20 countries will share their latest research on topics including 3D integration, bridge and chiplet integration, hybrid bonding, wafer-to-wafer and chip-to-wafer bonding, novel substrate materials, high-density RDL, next-generation interconnections, and warpage management of large panels. Also, large-package manufacturing, additive manufacturing, wearable and medical applications, AI/ML, and advanced RF and antenna design are on the agenda. Thermal management, interconnect reliability, advanced characterization, and process simulations, eco-friendly packaging, and secure designs will be discussed as well. Interactive sessions will focus on innovations in bonding, power delivery, optimization algorithms, specialized device packaging, and reliability testing. The 75th ECTC serves as a global platform for exploring cutting-edge advancements in microelectronic packaging, fostering innovation, and addressing industry challenges.

This year, the conference features a total of eleven special sessions with industry experts, including nine on Tuesday, each lasting 90 minutes. On Tuesday, two parallel sets of special sessions take place instead of one as in previous years. Rozalia Beica (Rapidus) and Habib Hichri (Ajinomoto Fine-Techno USA) chair the first session, which explores Ultra High-Density Interconnect Technologies. Mascha Gorchichko (Applied Materials) and Dishit Parekh (AMD) chair the second session, focusing on Hybrid Bonding. At 10:30 a.m., Richard Pitwon (Resolute Photonics Ltd) and Ajey Jacob (University of Southern California) discuss Quantum Advanced Packaging. Simultaneously, Jan Vardaman (TechSearch International), Zia Karim (Yield Engineering Systems), and Thom Gregorich (Zeiss) will present on Glass Core vs. RDL Interposers. In the afternoon, Vidya Jayaram (Chipletz) and Karan Bhangaonkar (Google) will chair a session on Advanced Materials for Co-Packaged Optics. For those interested in Fault and Failure Analysis in Chiplets, Yan Li (Samsung), Tae-Kyu Lee (Cisco), and Zhi Yang (Groq) simultaneously lead a dedicated session. The final two special session blocks include a discussion on Sub-THz Packaging for Communication and Radar, chaired by Maciej Wojnowski (Infineon Technologies AG) and Ivan Ndip (Fraunhofer IZM/Brandenburg University of Technology), as well as a session on Thermal Management for Power Delivery, chaired by Dwayne Shirley (Marvell) and Tiwei Wei (Purdue University).

Parallel to the special sessions, the Heterogeneous Integration Roadmap (HIR) workshop will be chaired by William Chen (ASE) and Ravi Mahajan (Intel). Four sessions are planned: IoT & AI at the Edge, moderated by Wei Chung Lo (ITRI) and Rockwell Hsu (Cisco); Advancing Heterogeneous Integration through Metrology & Ai, moderated by Chris Bailey (ASU) and Xuejun Fan (Lamar University); Integrating Photonics in HPC & Network Systems, moderated by Kanad Ghose (Binghamton Univ.) and John Shalf (LBL); and Advances in Panels, Substrates and Printed Circuit Boards moderated by William Chen (ASE) and Ravi Mahajan (Intel).

Tuesday evening offers additional opportunities to engage. Aakrati Jain (IBM) will lead a Young Professionals Networking Event from 6:45 p.m. to 7:45 p.m., featuring a new fish-bowl discussion format. Following this, Takashi Hisada and Yasumitsu Orii (both with Rapidus) will chair the IEEE EPS Seminar on User Perspectives of Chiplet Technology from 7:45 p.m. to 9:15 p.m.

On Wednesday morning, May 28, 2025, ECTC will feature a keynote presentation on Achieving Efficient Zettascale Compute in the AI Era by Sam Naffziger (AMD), invited by General Chair Florian Herrault (PseudolithIC, Inc.) The Student Engagement Program, chaired by Ibrahim Guven (Virginia Commonwealth University), will also take place throughout the day, welcoming undergraduate students from local universities and colleges. On Thursday, May 29, 2025, from 8:00 to 9:15 a.m., a Plenary Session on Emerging Advanced Power Delivery for the AI Computing Era will be chaired by Dongming He (Qualcomm) and Eric Beyne (imec). Additionally, an IEEE EPS President's panel titled ECTC at 75: Celebrating the Past, Innovating for the Future organized by IEEE EPS President Patrick Thompson (Texas Instruments) will be held on Friday morning, May 30, 2025.

The IEEE ITherm Conference is co-located with the 75th Anniversary ECTC and co-organizes 16 CEU-approved Professional Development Courses (PDCs). Organized by Kitty Pearsall and Jeffrey Suhling, these expert-led courses will be held on Tuesday, May 27, 2025.

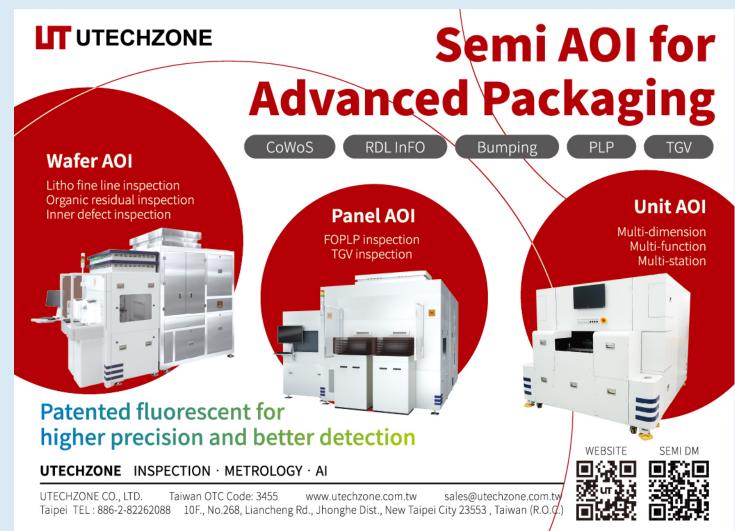

The ECTC Exhibits, running Wednesday, May 28, and Thursday, May 29, showcase cutting-edge technologies and products from over 100 leading companies in electronic components, materials, packaging, and services. Starting daily at 9 a.m., the exhibits provide excellent opportunities for networking during coffee breaks, luncheons, and evening receptions.

Whether you are an engineer, manager, student, or executive, ECTC offers unique experiences for everyone in the microelectronics packaging and components industry. I invite you to make your plans now to join us for the Anniversary 75th ECTC and to be a part of all the exciting technical and professional opportunities.

I want to thank our sponsors, exhibitors, authors, speakers, PDC instructors, session chairs, and program committee members, as well as all the volunteers who help make the Anniversary 75th ECTC a success. I look forward to meeting you at the Gaylord Texan Resort & Convention Center, Dallas, Texas, from May 27 to 30, 2025.

Przemysław Gromala 75th ECTC Program Chair pgromala@ieee.org

## Index

| ECTC Registration                | 3, 31, 32 |

|----------------------------------|-----------|

| General Information              | 3         |

| Hotel Information                |           |

| Conference Overview              | 4         |

| Tuesday Special Sessions         | 4         |

| Conference Panel Sessions        | 5, 6      |

| ECTC Morning Keynote Speaker     | 5         |

| 2025 IEEE EPS Seminar            | 5         |

| Luncheons and Evening Receptions | 6         |

| Executive and Program Committees |           |

| Professional Development Courses | 9-14      |

| Program Sessions                 | 15-30     |

| 2025 ECTC Exhibition             |           |

| Area Attractions                 |           |

|                                  |           |

## 75th ECTC ADVANCE REGISTRATION

## **Advance Registration**

# Online registration is available at www.ectc.net. For more information on registration rates, terms, and conditions see page 32.

Register by May 1, 2025 and save US\$100 or more! All registrations received thereafter are considered Door Registrations. Those who register in advance can print out their badges and pick up their registration packets at the ECTC Registration Desk in the Convention Center Lobby.

## **On-Site Registration Schedule**

Registration will be held in the Convention Center Lobby

Monday, May 26, 2025

12:00 Noon - 4:00 p.m.

Tuesday, May 27, 2025

6:45 a.m. - 7:45 p.m.\*

\*6:45 a.m. - 8:00 a.m.: Morning PDCs & morning ECTC Special Sessions only

Wednesday, May 28, 2025

6:45 a.m. - 4:00 p.m.

Thursday, May 29, 2025

7:00 a.m. - 4:00 p.m.

Friday, May 30, 2025

7:00 a.m. - 12:00 Noon

## The schedule for Tuesday will be rigorously enforced to prevent PDC attendees from being late for their courses.

## **General Information**

Conference organizers reserve the right to cancel or change the program without prior notice. The Gaylord Texan Resort & Convention Center, as well as ECTC, are both smoke-free environments.

## ITherm 2025

ITherm is co-located with ECTC! All ITherm sessions and exhibits will take place in the Gaylord Texan Resort & Convention Center. For more information about ITherm 2025 please visit https://www.ieee-itherm.net/.

## Loss Due to Theft

Conference management is not responsible for loss or theft of personal belongings. Security for each individual's belongings is the individual's responsibility.

## **ECTC Sponsors**

With over seven decades of history and experience behind us, ECTC is recognized as the premier semiconductor packaging conference and offers an unparalleled opportunity to build relationships with more than 2,000 individuals and more than 150 organizations committed to driving innovation in semiconductor packaging.

We have a limited number of sponsorship opportunities in a variety of packages to help get your message out to attendees. These include Platinum, Gold, Silver, Program, and several other sponsorship options that can be customized to your company's interest. If you would like to enhance your presence at ECTC and increase your impact with a sponsorship, please take a look at our sponsorship brochure on the website www.ectc.net under "Sponsors".

To sign-up for sponsorship or to get more details, please contact Alan Huffman at alan.huffman@ieee.org or +1-336-380-5124.

## **Hotel Accommodations**

Rooms for ECTC attendees have been reserved at the Gaylord Texan Resort & Convention Center. The special conference rate for a single/double occupancy room is:

### US \$229.00 per night

This price includes single or double occupancy in one room.

Please note these rooms are on a first come, first serve basis. If the conference rate is no longer available, attendees will be offered the next best price available.

Room reservations must be made directly with the hotel by May 1, 2025, at 5 p.m., Central Daylight Time (CDT), or until rooms run out, whichever comes first, to ensure our special conference rate. All reservations made after the cutoff date or after rooms run out will be accepted on a space and rate availability basis. If you need to cancel a reservation, please do so by 5 p.m. Central Time at least 5 days prior to arrival for a full refund.

Check-in time is 4 p.m. and check-out time is 11 a.m.

## Note about Hotel Rooms

Attendees should note that only reputable sites should be used to book a hotel room for the 2025 ECTC. Be advised that you may receive emails about booking a hotel room for ECTC 2025 from 3rd party companies. These emails and sites are likely scams and not to be trusted. **The only formal communication** ECTC will convey about hotel rooms will come in the form of ECTC e-blasts or ECTC emails from our Executive Committee or our IT system. **ECTC's only authorized site** for reserving a room is through our website (www.ectc.net). Should you have any questions about booking a hotel room please contact ECTC staff at: **registration@ectc.net**

### **Transportation Services**

There is no complimentary transportation to and from the hotel and airport. All attendees must make their own transportation arrangements to the hotel upon arriving at the airport.

## 75th ECTC CONFERENCE OVERVIEW

## 2025 Special Session on Ultra High Density Interconnect Technologies

Ultra High Density Interconnect Technologies and Supply Chain Readiness for AI & HPC

Tuesday, May 27, 2025, 8:30 a.m. – 10:00 a.m.

Chairs: Rozalia Beica, Rapidus and Habib Hichri, Ajinomoto Fine-Techno USA Corporation

Heterogeneous integration and chiplets will require fine line and space interconnects, as well as low warpage materials, to achieve the required performance for various applications in the rapidly evolving landscape of Artificial Intelligence (AI) and High-Performance Computing (HPC), which have significantly increased computational and memory needs. One of the critical areas that continues to have challenges in

the industry is advancing the interconnects at the organic substrate level, reason why various different approaches are being considered:

- Ultra-high density organic substrate (2.0D), bringing front-end of the line processes into the substrate/panel infrastructure to meet ultrafine Via/L/S (2/2/2 um and below).

- Building the organic substrate at wafer level (SOW)

- Hybrid substrates

Bringing the well-known redistribution lines (RDLs) to substrates using 2.xD technologies

Bringing glass substrates to address the needs for advanced interconnects and warpage issues for large size and complex substrates.

Each of these approaches have their own limitations and challenges. This session will discuss the different alternative technologies addressing the latest developments and remaining challenges, supply chain readiness to address the next generation of interconnects.

The session will comprise a panel of industry experts across the supply chain with global participation. Each panelist will provide a short presentation of their view on these technologies and supply chain readiness followed by a panel discussion.

Yu Hua Chen, Unimicron; Niranjan Khasgiwale, Applied Materials; Kuldip Johal, Atotech; Yoshio Nishimura, Ajinomoto; Monita Pau, Onto Innovation; Yoshio Takatsu, ORC Manufacturing Co., Ltd.

## 2025 Special Session on Hybrid Bonding

Hybrid Bonding (HB): to B, or not to B? Needs and challenges for the Next Decade

#### Tuesday, May 27, 2025, 8:30 a.m. - 10:00 a.m.

Chairs: Mascha Gorchichko, Applied Materials, Inc. and Dishit Parekh, AMD

Hybrid bonding is the key technology for high-density 3D integration and advanced packaging. In recent years, significant advancements were made in pitch scaling, die-to-die bonding, alternative materials, and low-temperature processes. However, there are still engineering and technological challenges that need to be addressed to expand the application domain, such as defectivity, metrology, design challenges, and

costs.

This panel aims to summarize the recent advancements in hybrid bonding identify the most pressing issues limiting the adoption of this technology for mainstream electronics, and outline the expected development of this technology for the next decade.

Sujin Ahn, Samsung Electronics; Liwei Wang, AMD; Chet Lenox, KLA Corporation; Anne Jourdain, imec; Masao Tomikawa, Toray Industries, Inc; Laura Mirkarimi, Adeia

## 2025 Special Session on Quantum Packaging

Quantum Photonic Advanced Packaging

Tuesday, May 27, 2025, 10:30 a.m. - 12:00 p.m.

Chairs: Richard Pitwon, Resolute Photonics Ltd. and Ajey Jacob, University of Southern California

As quantum technologies advance, the need for robust and scalable systems to support applications like Quantum Key Distribution (QKD) and quantum photonic computation becomes increasingly critical. These emerging technologies demand a sophisticated ecosystem capable of integrating high-fidelity quantum photonic systems into the quantum physical layer, where single or entangled photon qubits are conveyed and processed. Quantum photonic systems, by their nature, require exceptional precision and control at the quantum level, which necessitates the heterogeneous integration of diverse materials and technologies into a cohesive unit that functions seamlessly. This integration is vital for ensuring the accurate transmission and manipulation of quantum information, which is the cornerstone of quantum computing and secure quantum communication. In this session, we will explore the latest advances in the assembly and packaging of quantum photonic systems. The focus will be on how innovative packaging solutions can address the unique challenges posed by quantum technologies, such as minimizing photon loss, ensuring thermal stability, transduction schemes, and maintaining the coherence of quantum states. We will discuss how these packaging techniques are being developed to support the high volume manufacturing of quantum devices, enabling their widespread adoption of data centric industries.

Bernard Lee, Senko; Michael Fanto, Air Force Research Lab; Takahiro Kashiwazaki, NTT; Inna Krasnokutska, Xanadu Quantum Technologies Inc.

## 2025 Special Session on Glass Core vs. RDL Interposers

Glass Core vs. RDL Interposers: Ready for Prime-Time?

Tuesday, May 27, 2025, 10:30 a.m. – 12:00 p.m.

Chairs: Jan Vardaman, TechSearch International, Inc., Zia Karim, Yield Engineering Systems, and Thom Gregorich, Zeiss

Given the critical role of high-density substrates in the semiconductor industry, glass-core substrates and RDL interposer advantages have been discussed. With growing

demand for higher performance, larger devices, and increased interconnect density, where does each technology fit, what are the necessary steps to address the critical challenges faced by the entire industry?

This session will address economic and technical perspectives for high volume solutions, including design, materials, process/equipment, and metrology to meet product needs and reliability requirements. The session will include a moderator and six panelists.

Brett Wilkerson, AMD; Kathy Yan, TSMC; Duan Gang, Intel Corp.; Richard Bae, Samsung; Akira Tamura, FICT; Makoto Kouzuma, Toppan

### 2025 Special Session on Advanced Materials for Co-Packaged Optics

## Advanced Materials for Enabling Co-Packaged Optics Integration

## Tuesday, May 27, 2025, 1:30 p.m. – 3:00 p.m.

Chairs: Vidya Jayaram, Chipletz and Karan Bhangaonkar, Google

Modern computing techniques are pushing the boundaries for high performance requirements. Co-packaged optics emerged as the future of microelectronics packaging, integrating optics and electronics on a single substrate, to meet the computing and communication demands for high bandwidth at low power. Although there are numerous challenges in realizing the optical co-packaging technology,

what comes along are great opportunities for foundries, IDMs and OSATs. Materials and processes play a key role in enabling this disruptive technology. Thus, this special session will invite industry leaders to share their insight about the innovations, challenges and future needs in realizing CPO technology.

Christopher Striemer, AIM Photonics; Padraic Morrissey, Tyndall Institute; Mark Gerber, ASE; Kumar Abhishek Singh, Intel; Rena Huang, Rensselaer Polytechnic Institute

#### 2025 Special Session on Fault and Failure Analysis in Chiplets

### Advances in Chiplets: Tackling Fault Isolation and Failure Analysis in Heterogeneous Integration

#### Tuesday, May 27, 2025, 1:30 p.m. – 3:00 p.m.

Chairs: Yan Li, Samsung, Tae-Kyu Lee, Cisco Systems, Inc., and Zhi Yang, Groq

By providing timely feedback data for effective failure root cause investigation, problem solving proposal and validation, process technology improvement, yield enhancement, and

reliability risk assessment, Fault Isolation (FI) and Failure Analysis (FA) play a crucial role during the technology development of Heterogeneous Integration, which is the leading advanced packaging technology developed to meet the High-Performance Computing (HPC) and Artificial Intelligence (AI) market demands of ever higher performance, lower power consumption, wider memory bandwidth with reduced latency. During the panel discussion, experts from both industry and academia will discuss the technology gaps and novel methodologies and techniques in FI and FA of Heterogeneous Integration.

Dr. Lihong Cao, ASE; Dr. Wenbing Yun, Sigray, Dr. Bernice Zee, AMD Singapore; Prof. Navid Asadi, University of Florida; Yaw S. Obeng, NIST; Dr. Thomas Rodgers, Zeiss

#### 2025 Special Session on Thermal Management for Power Delivery

Thermal Management Solutions for Next-Generation Backside Power Delivery

#### Tuesday, May 27, 2025, 3:30 p.m. - 5:00 p.m.

Chairs: Dwayne Shirley, Marvell Semiconductor, Inc. and Tiwei Wei, Purdue University

The increasing power density and thermal challenges in advanced semiconductor packaging have led to the development of backside power delivery (BPD) technology. BPD relocates the power delivery network from the frontside to the backside of a silicon wafer, enhancing power efficiency, performance, and design flexibility. However, this technology also introduces new thermal management challenges, including higher

thermal densities and the need for innovative cooling solutions.

This special session aims to bring together experts from academia and industry to discuss the latest advancements and challenges in thermal management solutions for next-generation BPD.

Dureseti Chidambarrao, IBM; Muhannad S Bakir, GA Tech; Herman Oprins, imec; Rongmei Chen, Peking University

2025 Special Session on Sub-THz Packaging for Communication and Radar

Advancements in mmWave and Sub-THz Packaging for Communication and Radar Applications

#### Tuesday, May 27, 2025, 3:30 p.m. - 5:00 p.m.

Chairs: Maciej Wojnowski, Infineon Technologies AG and Ivan Ndip, Fraunhofer IZM/Brandenburg University of Technology

In this session, experts from industry and academia will present the latest developments in high-frequency packaging and system integration at mmWave and sub-THz frequency bands. The session will begin with presentation of emerging wireless communication and radar sensing applications in these bands, and resulting challenges and opportunities for RF packaging. Advanced system integration

platforms using different high-frequency materials for these applications will be presented. Emphasis will be laid on characterizing the packaging materials and interconnects at these very high frequencies as well as on co-design and co-simulation techniques. The session will conclude with presentation and discussion of concrete examples of latest developments of novel interconnects, components and wireless modules for 6G communication and radar applications at mmWave and sub-THz bands.

Madhavan Swaminathan, Penn State University; Xiao Sun, imec; Parisa Aghdam, Ericsson; Atom Watanabe, IBM T.J. Watson Research Center

#### 2025 IEEE EPS Heterogeneous Integration Roadmap (HIR) Workshop

Four Technical Sessions, spanning morning and afternoon of Tuesday, May 27, 2025

#### Chairs: Ravi Mahajan, Intel Corporation and William Chen, ASE

Review

IoT & AI at the Edge Advancing Heterogeneous Integration

HIR Welcome, Introduction & Agenda

through Metrology & Al

Integrating Photonics in HPC & Network Systems

Advances in Panels, Substrates and Printed Circuit Boards

#### 2025 ECTC Young Professional Networking Event

#### Tuesday, May 27, 2025, 6:45 p.m. – 7:45 p.m.

#### Chair: Aakrati Jain, IBM

Join us for an invaluable opportunity to connect with industry leaders and fellow emerging talents! Tailored specifically for young professionals, including current graduate students, this event is crafted with your needs in mind. Engage in dynamic interactions with senior EPS members and professionals through a series of active and engaging activities. Seize the chance to delve deeper into packaging-related topics, pose career questions, and connect with industry professionals for a valuable learning experience.

### 2025 IEEE EPS Seminar on Chiplet Technology

User Perspective of Chiplet Technology Tuesday, May 27, 2025, 7:45 p.m. – 9:15 p.m.

#### Chairs: Takashi Hisada, Rapidus and Yasumitsu Orii, Rapidus

Styled as a start-up competition, this session looks at next generation materials and companies.

The EPS Seminar organized by the technical committee TC6 (High-Density Substrate and Board) of IEEE EPS will discuss the current status and future evolution of chiplet technology from the end use perspective. We will have 5 panelists from various segments such

as high-end computing, automotive and network. Each panelist will give a short talk presenting insights on technical trends/challenges including optically integrated chiplet, application requirements, user's expectation of chiplet technology, followed by a panel discussion.

Raja Swaminathan, AMD; Takao Iwaki, ASRA (MIRISE Technologies); Takashi Saida, NTT: Omar Bchir, Qualcomm; Carlos Macian Ruiz, Marvell; Sam Karikalan, Broadcom.

## 2025 ECTC Keynote Talk

Achieving Efficient Zettascale Compute in the AI Era

Wednesday, May 28, 2025, Time: 8:00 a.m. - 9.15 a.m.

Chair: Florian Herrault, PseudolithIC Inc. Speaker: Sam Naffziger, AMD

The demand for compute and the energy to power it is increasing faster than ever before in our industry. Meeting the challenge of delivering this processing power in the Al era requires holistic innovation from the device to the datacenter level. It starts with integrating highly optimized, domainspecific accelerators with advanced 2.5D and 3.5D packaging to maximize the amount of compute within the most efficient, local

communication domain. These accelerators and other system components must be packed into tightly integrated sleds that minimize losses and power for high-speed communication while taking advantage of workload-aware power management. Scaling to the rack and datacenter level will require many advances in signaling technologies, rack design, and power optimization to enable the training and inference computation required by the most demanding frontier models. This talk will cover these trends and key technologies that will power compute growth at a scale we wouldn't have conceived of just a few short years ago.

## 2025 ECTC Student & Start-Up Innovation Challenge

## Future Forward: The Student & Start-up Innovation Challenge!

### Wednesday, May 28, 2025, 6:30 p.m. - 8:30 p.m.

Chairs: Rozalia Beica, Rapidus, Farhang Yazdani, BroadPak, and Jason Rouse, Taiyo America, Inc.

This session is organized as a competition and will have competing pitches of both student teams and start-ups followed by deliberation of a jury panel, awards announcements, and

networking session. We will have three student pitches and six start-up pitches (7 min. each) followed by Q&A from the jury panel. The Q&A will be open to the audience. The jury will deliberate and choose the winning student team and start-up. The session will end with the announcement of the winners and a networking session.

## 2025 Plenary Session on Advanced Power Delivery for AI

**Emerging Advanced Power Delivery for the AI Computing Era** Thursday, May 29, 2025, 8:00 a.m. - 9:15 a.m.

Chairs: Dongming He, Qualcomm Technologies, Inc. and Eric Beyne, imec

Al computing introduces significant challenges for energy consumption and thermal management. Optimal power delivery network (PDN) is crucial for CPU, GPU and NPU power and performance. Advanced PDN solutions such as silicon deep trench capacitor (DTC) and integrated stacked capacitor (ISC), integrated voltage regulator (IVR), silicon metal-insulator-metal (MIM) capacitor and thin film inductor, backside

power rail, etc., have been explored, developed, and adopted. Industry leaders and experts will share their views on benefit and tradeoff for these building blocks, integration challenges and opportunities at silicon device, package and board levels plus system technology co-optimization (STCO).

Kaladhar Radhakrishnan, Intel Corp.; Harrison Chang, ASE Global; PR. Chidi Chidambaram, Qualcomm; Raja Swaminathan, AMD; Chuei-Tang Wang, TSMC

## **2025 IEEE EPS President's Panel**

ECTC at 75: Celebrating the Past, **Innovating for the Future**

Friday, May 30, 2025, 8:00 a.m. - 9:15 a.m.

## **Chair: Patrick Thompson, Texas Instruments**

Join EPS/ECTC luminaries as they share: · Early memories of ECTC and key innovations that revolutionized the industry

- What's happening now that is exciting to them

- Their thoughts on what we'll be reviewing at the 100th ECTC

### Luncheons

ECTC offers a daily luncheon (Tuesday - Friday) for all attendees registered for the full conference. The QR code on your registration badge will scan you into lunch. Please come and enjoy time with other attendees and colleagues in the industry! Lunch times vary, see below for specific details for each day.

| Tuesday:   | 12:00 Noon – 1:15 p.m.                                                                                                                                                              |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Wednesday: | 12:45 p.m. – 2:00 p.m.                                                                                                                                                              |

| Thursday:  | 12:45 p.m. – 2:00 p.m. – Sponsored<br>by: The IEEE Electronics Packaging<br>Society (EPS)                                                                                           |

| Friday:    | 12:45 p.m. – 2:00 p.m. – Don't miss<br>out on this lunch! We will be raffling<br>off a number of prizes including<br>a hotel stay, free conference<br>registrations, and many other |

### **ECTC Student Reception**

industry gadgets!

Tuesday, May 27, 2025 • 5:00 p.m. - 6:00 p.m. Hosted by Texas Instruments, Inc.

Students, have you ever wondered what career opportunities exist in the industry **INSTRUMENTS** and how you could use your technical skills and innovative talent? If so, you are invited

to attend the ECTC Student Reception, where you will have the opportunity to talk to industry professionals about what helped them be successful in their first job search and reach their current positions. You will have the chance to enjoy good food and network with industry leaders and achievers. Don't miss the opportunity to interact with people that you might not have the chance to meet otherwise!

### **General Chair's Speakers Reception**

Tuesday, May 27, 2025 • 6:00 p.m. - 7:00 p.m. (by invitation only)

## **Exhibitor Reception**

Wednesday, May 28, 2025 • 5:30 p.m. - 6:30 p.m.

## **EPS Chapter Officer Meet and Greet**

Thursday, May 29, 2025 • 7:00 a.m. - 8:00 a.m. (online by invitation)

With 46 EPS Chapters all over the world, this once-a-year event is a great opportunity for all chapter officers to meet with fellow officers face to face and to learn about successes and best practices.

> Program Director: Andrew Tay Regions 1-7 and 9 (Americas): Annette Teng Region 8 (Europe and Africa): Steffen Kroehnert Region 10 (Asia): Wong Shaw Fong

## 75th ECTC Gala Reception

Thursday, May 29, 2025 • 7:30 p.m. Hosted by Koh Young Technology

Please note: Badges are required for the duration of the conference including all evening functions and receptions.

Executive Committee Chair

Florian Herrault PseudolithIC, Inc. floherrault@gmail.com

Vice-General Chair Michael Mayer University of Waterloo mmayer@uwaterloo.ca

Program Chair Przemysław Gromała Robert Bosch GmbH pgromała@ieee.org

Assistant Program Chair Bora Baloglu Intel Corporation borabal@ieee.org

Jr. Past General Chair . Karlheinz Bock TU Dresden karlheinz.bock@tu-dresden.de

Sr. Past General Chair Ibrahim Guven Virginia Commonwealth University iguven@vcu.edu

Sponsorship Chair Alan Huffman L3Harris alan.huffman@ieee.org

Finance Chair Patrick Thompson Texas Instruments, Inc. patrick.thompson@ti.com

Publications Chair Henning Braunisch Intel Corporation braunisch@ieee.org

Publicity Chair Eric Perfecto IBM Research eric.perfecto.us@ieee.org

Treasure Tom Reynolds T3 Group LLC t.reynolds@ieee.org

Exhibits Chair Sam Karikalan Broadcom Limited samkarikalan@ieee.org

IT Coordinator Tanja Braun Fraunhofer IZM tanja.braun@izm.fraunhofer.de

Professional Development Course Chair Kitty Pearsall Capstan Technologies kitty.pearsall@gmail.com

Conference Management Lisa Renzi Ragar Renzi & Company, Inc. Irenzi@renziandco.com

IEEE EPS Representative Annette Teng AIM Photonics ateng@sunypoly.edu

Packaging Technologies

*Chair* Mike Gallagher DuPont Electronic Materials michael.gallagher@dupont.com

Assistant Chair Peng Su Juniper Networks pensu@juniper.net

Lihong Cao Advanced Semiconductor Engineering, Inc. lihong.cao@aseus.com

Jie Fu Apple Inc. fujie6@gmail.com

Glenn Ning Ge TetraMem glenn.ge@tetramem.com

Kuldip Johal MKS Instruments - MSD kuldip.johal@atotech.com

Sam Karikalan Broadcom Limited samkarikalan@ieee.org

Beth Keser Zero ASIC bethk@kesers.com

Young-Gon Kim Renesas Electronics America young.kim.jg@renesas.com

Andrew Kim Apple hkim34@apple.com

John Knickerbocker IBM Corporation knickerj@us.ibm.com

Steffen Kroehnert ESPAT Consulting, Germany steffen.kroehnert@espat-consulting.com

Albert Lan Applied Materials Albert\_Lan@amat.com

John H. Lau Unimicron Technology Corporation John\_Lau@Unimicron.com

Jaesik Lee SK Hynix USA Jaesik.Lee@us.skhynix.com Kyu-Oh Lee

Intel Corporation kyu-oh.lee@intel.com

Markus Leitgeb AT&S m.leitgeb@ats.net Monita Pau

Onto Innovation monita.pau@ontoinnovation.com

Luu Nguyen Psi Ouantum Inguyen@psiquantum.com

Raj Pendse Facebook rajd@fb.com Min Woo Rhee

Samsung mw.daniel.lee@gmail.com

Subhash L. Shinde Notre Dame University sshinde@nd.edu

Joseph W. Soucy Draper Laboratory jsoucy@draper.com

Eric Tremble Marve etremble@marvell.com

Kuo-Chung Yee Taiwan Semiconductor Manufacturing Corporation, Inc. kcyee@tsmc.com

Applied Reliability Vikas Gupta

ASE US. Inc Gvikas.Gupta@outlook.com Assistant Chair

Sandy Klenge Fraunhofer Institute for Microstructure of Materials and

sandy.klengel@imws.fraunhofer.de Seung-Hyun Chae

SK Hynix seunghyun1.chae@sk.com

Tz-Cheng Chiu National Cheng Kung University tcchiu@mail.ncku.edu.tw

Deepak Goyal Intel Corporation deepak.goval@intel.com

Nokibul Islam JCET Group Nokibul.islam@jcetglobal.com

Choong-Un Kim The University of Texas at Arlington choongun@uta.edu

Tae-Kyu Lee Cisco Systems, Inc. taeklee@cisco.com

Yan Li Samsung Semiconductor Inc. yan.ali@samusung.com

Pilin Liu Intel Corporation pilin.liu@intel.com

Varughese Mathew NXP Semiconductors varughese.mathew@nxp.com

Keith Newman AMD keith.newman@amd.com

Donna M. Noctor Nokia

donna.noctor@nokia.com S. B. Park Binghamton University

sbpark@binghamton.edu Scott Savage Medtronic Microelectronics Center

scott.savage@medtronic.com

Jeffrey Suhling Auburn University isuhling@auburn.edu Paul Tiner

Texas Instruments p-tiner@ti.com

Pei-Haw Tsao Mediatek ph.tsao@mediatek.com

Dongji Xie NVIDIA Corporation dongjix@nvidia.com

## Assembly & Manufacturing Technology

Paul Houston Engent paul.houston@engentaat.com

Assistant Chair Christo Bojkov UT Dallas cbojkov.ectc@gmail.com Sai Ankireddi

Maxim Integrated sai.ankireddi@alumni.purdue.edu Pascale Gagnon IBM Canada

pgagnon@ca.ibm.com Mark Gerber Advanced Semiconductor Engineering, Inc.

mark.gerber@aseus.com

Omkar Gupte AMD Omkar.Gupte@amd.com Timo Henttonen

Microsoft timo.henttonen@microsoft.com

Habib Hichri Ajinomoto Fine-Techno USA Corporation hichrih@ajiusa.com

Li Jiang Texas Instruments I-jiang1@ti.com

Zia Karim Yield Engineering Systems ZKarim@yes.tech

Wei Koh Pacrim Technology kohmail@gmail.com

Siddarth Krishnan Applied Materials sidkris@gmail.com Wenhao (Eric) Li

Intel Corporation wenhao.li@intel.com Venkata Mokkapati

AT & S v.mokkapati@ats.net

Jae-Woong Nah IBM Corporation jnah@us.ibm.com Valerie Oberson

IBM Canada Ltd voberson@ca.ibm.com

Jason Rouse Taiyo America, Inc. jhrouse@taiyo-america.com Andy Tseng Qualcomm Technologies, Inc.

andytseng2000@yahoo.com Jobert Van Eisden MKS Instruments Jobert.van-Eisden@atotech.com

Jan Vardaman TechSearch International

ian@techsearchinc.com Shaw Fong Wong

Intel Corporation shaw.fong.wong@intel.com Jin Yang Samsung Electronics jin1.yang@ieee.org

Cong Zhao Meta zhaocong@meta.com

Ralph Zoberbier Evatec AG ralph.zoberbier@evatecnet.com

### Interactive Presentations

*Chair* Frank Libsch IBM Corporation libsch@us.ibm.com

Assistant Chair Karan Bhangaonkar Google karanbhangaonkar@outlook.com

Rao Bonda Amkor Technology rao.bonda@amkor.com

Joshua Dillon Marvell Govt. Solutions JoshuaFDillon@gmail.com

Mark Eblen Kyocera International SC mark.eblen@kyocera.com

Mohammad Enamul Kabir Intel Corporation enamul101b@yahoo.com

Ibrahim Guven Virginia Commonwealth University iguven@vcu.edu

Alan Huffman L3Harris alan.huffman@ieee.org Jeffrey Lee iST-Integrated Service Technology Inc. jeffrey\_lee@istgroup.com

Stephen Lee NXP Semiconductors stephen.lee@nxp.com Michael Mayer University of Waterloo

mmayer@uwaterloo.ca

Intel Corporation saikat.mondal@intel.com

rpaladhi01@gmail.com

Binghamton University mpoliks@binghamton.edu

Patrick Thompson

Kristina Young

ou.li@aseus.com

gang.duan@intel.com

David Danovitch

Takafumi Fukushima

Thom Gregorich

Yoshihisa Kagawa

Kangwook Lee SK Hynix steward.lee@sk.com

packaging@yahoo.com

Changqing Liu Loughborough University cliu@lboro.ac.uk

lo@itri.org.tw

Nathan Lowe

James Lu

luj@rpi.edu

Consultant nplower@hotmail.com

Rensselaer Polytechnic Institute

Vempati Srinivasa Rao IME A-star vempati@ime.a-star.edu.sg

Katsuyuki Sakuma

ksakuma@us.ibm.com

Jean-Charles Souriau CEA Leti

chtungc@tsmc.com

Purdue University tiwei@purdue.edu

Matthew Yao

GE Aerospace matthew.yao@ge.com

Dingyou Zhang

Broadcom Inc.

Chaoqi Zhang Qualcomm Technologies, Inc. chaoqi.gt.zhang@gmail.com

dingyouzhang.brcm@gmail.com

7

Tiwei Wei

Chuan Seng Tan Nanyang Technological University tancs@alum.mit.edu

Chih-Hang Tung Taiwan Semiconductor Manufacturing Company

jcsouriau@cea.fr

IBM Research

Li Li

Infinera

Carl Zeiss

Tohoku University fukushima-tak@tohoku.ac.jp

tmgregorich@gmail.com

Sony Yoshihisa.Kagawa@sony.com

Seung Yeop Kook GlobalFoundries seung-yeop.kook@globalfoundries.com

Wei-Chung Lo ITRI, Industrial Technology Research Institute

Jian Cai Tsinghua University jamescai@tsinghua.edu.cn

C. Key Chung TongFu Microelectronics Co. Ltd. chungckey@hotmail.com

University of Sherbrooke David.Danovitch@USherbrooke.ca

Bernd Ebersberger Infineon Technologies bernd.ebersberger@infineon.com

Assistant Chair

Gang Duan Intel

Jian Cai

Chair

Texas Instruments, Inc.

Interconnections

patrick.thompson@ti.com

Synopsys Inc kristina.youngfisher@gmail.com

Ou Li Advanced Semiconductor Engineering, Inc.

Saikat Mondal

Pavel Roy Paladhi NVIDIA

Mark Poliks

Wei Zhou Micron zhouwei@micron.com

#### Materials & Processing

Qianwen Chen Broadcom wendy.chen@broadcom.com

Assistant Chair Vidya Jayaram Intel Corporation vidya.jayaram@intel.com

Tanja Braun Fraunhofer IZM tanja.braun@izm.fraunhofer.de

Yu-Hua Chen Unimicron yh\_chen@unimicron.com

Jae Kyu Cho GlobalFoundries jaekyu.cho@globalfoundries.com

Bing Dang IBM Corporation dangbing@us.ibm.com

Gibran Liezer Esquenazi LODX gibranesquenazi@gmail.com

Lewis Huang Senju Electronic lewis@senju.com.tw

C. Robert Kao National Taiwan University crkao@ntu.edu.tw

Alvin Lee Brewer Science alee@brewerscience.com

Yi Li Intel Corporation vi.li@intel.com

Ziyin Lin Intel Corporation ziyin.lin@intel.com

Yan Liu Medtronic Inc. USA yan.x.liu@medtronic.com

Mikel Miller Apple Inc. mikel\_miller@apple.com

Praveen Pandoiirao-S Johnson & Johnson praveen@its.ini.com

Mark Poliks Binghamton University mpoliks@binghamton.edu

Dwayne Shirley Marvell Semiconductor, Inc. shirley@ieee.org

Ivan Shubin Raytheon Technologies ishubin@gmail.com

Bo Song HP Inc. bo.song@hp.com

Yoichi Taira Keio University taira@appi.keio.ac.ip

Frank Wei DISCO Corporation frank\_w@discousa.com

Lingyun (Lucy) Wei Dupont lingyun.wei@dupont.com

Kimberly Yess Brewer Science kyess@brewerscience.com

Myung Jin Yim Apple Inc. myung27@hotmail.com

Hongbin Yu Arizona State University yuhb@asu.edu

Zhangming Zhou Qualcomm zhou.zhming@gmail.com

Electrical Design & Analysis (ex RF, High-Speed Components & Systems) Chair

Jaemin Shin Qualcomm Technologies, Inc. jaemins@qti.qualcomm.com

Assistant Chair Hideki Sasaki Rapidus Corporation hideki.sasaki@rapidus.co.jp

Amit P. Agrawal Microchip Technologies amit.agrawal@amd.com

Kemal Aygun Intel Corporation kemal.aygun@intel.com

8

Eric Beyne imec eric.beyne@imec.be

Prem Chahal Michigan State University chahal@msu.edu

Harrison Chang ASE harrison\_chang@aseglobal.com

Zhaoqing Chen IBM Corporation zhaoqing@us.ibm.com

Charles Nan-Cheng Chen Shanghai Jiao Tong University hi2018.charles@gmail.com Craig Gaw NXP Semiconductor

c.a.gaw@ieee.org Xiaoxiong (Kevin) Gu Metawave xgu@ieee.org

Rockwell Hsu Cisco Systems, Inc. rohsu@cisco.com

Lianjun Liu NXP Semiconductor, Inc. Iianjun.liu@NXP.com

Sungwook Moon Samsung Electronics sw2013.moon@samsung.com

Rajen M Murugan Texas Instruments r-murugan@ti.com

Ivan Ndip Fraunhofer IZM/Brandenburg University of Technology (BTU) ivan.ndip@izm.fraunhofer.de

P. Markondeya Raj Florida International University mpulugur@fiu.edu

Li-Cheng Shen Universal Scientific Industrial Co. Ltd. (USI) Ii-cheng\_shen@usiglobal.com

Srikrishna Sitaraman Marvell Technology srikrishna.sitaraman@gmail.com

Xiao Sun IMEC xiao.sun@imec.be

Manos M. Tentzeris Georgia Institute of Technology etentze@ece.gatech.edu

Chuei-Tang Wang Taiwan Semiconductor Manufacturing Company (TSMC) ctwang10492@hotmail.com

Maciej Wojnowski Infineon Technologies AG maciej.wojnowski@infineon.com

Yong-Kyu Yoon University of Florida ykyoon@ece.ufl.edu

Thermal/Mechanical Simulation & Characterization Chair Karsten Meier

TU Dresden karsten.meier@tu-dresden.de

Assistant Chair Rui Chen Eastern Michigan University rchen7@emich.edu

Christopher J. Bailey Arizona State University christopher.i.bailey@asu.edu

Liangbiao Chen On Semiconductor bill.chen@onsemi.com

Kuo-Ning Chiang National Tsinghua University / Department of Power Mechanical Engineering knchiang@pme.nthu.edu.tw

Ercan (Eric) Dede Toyota Research Institute of North America eric.dede@tovota.com

Xueiun Fan Lamar University xuejun.fan@lamar.edu Przemyslaw Gromala

Robert Bosch GmbH pgromala@ieee.org

Pradeep Lall Auburn University Iall@auburn.edu

Chang-Chun Lee National Tsinghua University (NTHU) cclee@pme.nthu.edu.tw Guangxu Li

Texas Instruments guangxu3559@gmail.com

Ruiyang Liu TeraDAR Inc. ruiyang.liu9@gmail.com

Yong Liu ON Semiconductor yong.liu@onsemi.com

Erdogan Madenci University of Arizona madenci@email.arizona.edu

Tony Mak Wentworth Institute of Technology tmak@ieee.org Patrick McCluskey University of Maryland mcclupa@umd.edu

Jiamin Ni IBM nijiamin8910@gmail.com

Erkan Oterkus University of Strathclyde erkan.oterkus@strath.ac.uk

Suresh K. Sitaraman Georgia Institute of Technology suresh.sitaraman@me.gatech.edu

Wei Wang Qualcomm Technologies, Inc. weiwang.cu@gmail.com

Zhi Yang Groq zyang@groq.com

Ning Ye Western Digital ning.ye@wdc.com G. Q. (Kouchi) Zhang Delft University of Technology (TUD) g.q.zhang@tudelft.nl

Xiaowu Zhang Institute of Microelectronics (IME) xiaowu@ime.a-star.edu.sg

Tieyu Zheng Microsoft Corporation tizheng@microsoft.com

Jiantao Zheng Hisilicon zheng,jiantao@hisilicon.com

Photonics *Chair* Takaaki Ishigure Keio University ishigure@appi.keio.ac.jp

Assistant Chair Christopher Striemer AIM Photonics cstriemer@gmail.com

Ankur Agrawal Intel Corporation

ankur.agrawal@intel.com Stephane Bernabe CEA Leti stephane.bernabe@cea.fr

Surya Bhattacharya bhattass@ime.a-star.edu.sg

Christopher Bower X-Display Company, Inc. chris@xdisplay.com

Nicolas Boyer Ciena nboyer@ciena.com

Lars Brusberg Corning brusbergl@corning.com

Mark Earnshaw Nokia mark.earnshaw@nokia-bell-labs.com

Gordon Elger Technische Hochschule Ingolstadt gordon.elger@thi.de

Z Rena Huang Rensselaer Polytechnic Institute zrhuang@ecse.rpi.edu

Ajey Jacob University of Southern California (USC) ajey@isi.edu

Aditya Jain Lightmatter ajain@lightmatter.co

Soon Jang ficon TEC USA soon.jang@ficontec.com

Harry G. Kellzi Micropac Industries harrykellzi@micropac.com Hidevuki Nasu

Furukawa Electric hidevuki.nasu@furukawaelectric.com

Richard Pitwon Resolute Photonics I td richard.pitwon@resolutephotonics.com

Vivek Raghuraman Broadcom Corporation vivek.raghuraman@gmail.com Dadi Setiadi Lightelligence dadi.setiadi@lightelligence.ai

Hiren Thacker Cisco Systems hithacke@cisco.com

Yutong Wu TSMC

ytwux@tsmc.com

Ping Zhou LDX Optronics, Inc.

Chair Xinpei Cao Henkel Corporation

xinpei.cao@henkel.com

Corning OkoroC@corning.com

Siemens Healthineers Isaac.abothu@siemens-healthineers.com

TU Dresden karlheinz.bock@tu-dresden.de

Benson Chan Binghamton University chanb@binghamton.edu

Vaidyanathan Chelakara

Cisco cvaidy@cisco.com

Rabindra N. Das MIT Lincoln Labs

Mariia Gorchichko

rabindra.das@ll.mit.edu

Applied Materials maria.gorchichko@gmail.com

Dongming He Qualcomm Technologies, Inc.

dhe@ati.aualcomm.com

Florian Herrault PseudolithIC, Inc floherrault@gmail.com

Jae-Woong Jeong KAIST

jjeong1@kaist.ac.kr

tengfei.jiang@ucf.edu

ih.kim@wsu.edu

Santosh Kudtarkar

Kevin J. Lee Qorvo Corporation

kevin|.Lee@gorvo.com

Zhuo Li Fudan University zhuo\_li@fudan.edu.cn

Yang Liu

Ran Tao

ran.tao@nist.gov

Hongqing Zhang IBM Corporation zhangh@us.ibm.com

*Chair* Kitty Pearsall Capstan Technologies

kitty.pearsall@gmail.com

Assistant Chair

Jeffrey Suhling Auburn University

isuhling@auburn.edu

Nokia Bell Labs

Dishit Parekh

yang3d@gmail.com

dishit.parekh@intel.com

Jintang Shang Southeast University shangjintang@hotmail.com

W. Hong Yeo Georgia Institute of Technology whyeo@gatech.edu

National Institute of Standards and Technology

Professional Development Courses

C. S. Premachandran GlobalFoundries 319prem@gmail.com

Tengfei Jiang University of Central Florida

Hee Seok Kim University of Washington Tacoma heeskim@uw.edu

Analog Devices santosh.kudtarkar@analog.com

Jong-Hoon Kim Washington State University Vancouver

Isaac Robin Abothu

Karlheinz Bock

Assistant Chair Chukwudi Okoro

pzhou@ldxoptronics.com

**Emerging Technologies**

Masao Tokunari IBM Corporation tokunari@jp.ibm.com Stefan Weiss

II-VI Laser Enterprise GmbH stefan.weiss@II-VI.com

## PROFESSIONAL DEVELOPMENT COURSES

## Tuesday, May 27, 2025

Kitty Pearsall, Chair Capstan Technologies kitty.pearsall@gmail.com +1-512-845-3287

Jeff Suhling, Assistant Chair Auburn University jsuhling@auburn.edu

## MORNING COURSES 8:00 a.m. — 12:00 Noon

## 1. HIGH RELIABILITY SOLDERING IN SEMICONDUCTOR PACKAGING

Course Leader: Ning-Cheng Lee – ShinePure Hi-Tech

## **Course Description:**

Semiconductor soldering is much more delicate and is critical for reliability of devices. The course covers the critical parameters governing the reliability for soldering in semiconductor packaging. The reliability discussed includes parameters affecting the intermetallic compounds (IMC), voiding, electromigration, low-temperature soldering, high-temperature soldering, and electrochemical migration under a variety of material combinations. The failure modes are discussed in detail, with preferred choices of materials and designs recommended.

## **Course Outline:**

- 1. IMC Effect of Cu Pad Grain Size on IMC

- 2. IMC Interaction of Cu and Ni

- 3. IMC Effect of Base Metal Co-P on IMC

- 4. Voiding Effect of Solder Form on Voiding

- Voiding Effect of Joint Height, Temperature, Electrical, Mechanical on Kirkendall Voiding

- 6. Voiding Effect of Cu Structure on Kirkendall Voids

- 7. Electrochemical Migration (ECM)

- 8. Electromigration

- 9. LTS Bi-Rich Whisker Growth

- 10. LTS TCT Reliability of LTS

- 11. LTS Collapse of LTS

- LTS Deposition, Hot Tear, Bi Stratification of LTS

- 13. LTS Hot Tear of Homogeneous LTS BiSn - Effect of Profile

- 14. LTS Drop Test of LTS

- 15. HTS TLPB (Transient Liquid Phase Bonding)

## **IMPORTANT NOTICE**

Anyone taking PDC courses, please register on-line in advance to prevent door registration delays.

## Who Should Attend:

Anyone who cares about achieving high reliability solder joints for semiconductor packaging and wants to know how to achieve it should take this course

## 2. PHOTONIC TECHNOLOGIES FOR COMMUNICATION, SENSING, AND DISPLAYS

Course Leader: Torsten Wipiejewski – Huawei Technologies

## **Course Description:**

This course will provide an overview on the various photonic technologies that enable optical communication, optical sensing, and modern display applications. These applications are key for the information and communication technology of today and pave the way to the future. High-speed optical communication from board level in data centers to long haul transmission requires photonic components with high speed and high reliability. We will discuss the main components such as laser diodes of various types, high-speed optical modulators and photodetectors as well as integration schemes such as photonic integrated circuits PICs and packaging aspects. Photonic technologies are also widely used as sensors for various applications including health monitoring. One key advantage is the potential for noninvasive measurements that facilitates the usage by end-users without specific medical knowledge. Optical sensor packaging should provide high accuracy solutions at low cost. Displays are the main media nowadays for bringing information to people. They range in size from smart watches to smart phones, laptops and tablets all the way to large screen TVs and video walls. We review current technologies and new developments such as guantum dots and micro-LEDs. In particular, micro-LEDs for large size displays require novel assembly technologies.

## **Course Outline:**

- 1. Fundamental Properties of Photonic Components

- 2. Light Sources (LEDs, Laser Diodes, VCSELs)

- 3. Transmitter and Receiver Components in Optical Communication Systems (Lasers, Modulators, Photodetectors)

- 4. Optical Modules, Monolithic and Hybrid Integration, Packaging.

- 5. Optical Sensing Elements and Applications (Spectrometers, Light Sources, Photoacoustic Sensors, Frequency Combs)

- 6. Display Technologies: Liquid Crystal Displays (LCD), Organic Light Emitting Diode Displays (OLED), Quantum Dot Emissive Layers, Micro-LED Displays Made by Chiplet Mass Transfer, and Bonding

- 7. Summary and Outlook

## Who Should Attend:

The course addresses engineers, scientists, and students who would like to get a general overview on various photonics technologies used in today's products and future developments. The aim is to describe which photonic technologies can be used in various applications and what current limitations are as well as potential technology breakthroughs.

## 3. FROM WAFER TO PANEL LEVEL PACKAGING

## Course Leaders: Tanja Braun and Piotr Mackowiak – Fraunhofer IZM

## **Course Description:**

Wafer and Panel Level Packaging are two of the dominating trends in microelectronics packaging. Both approaches with different flavors as RDL-last face-up or face-down have reached maturity and are introduced in high volume manufacturing. Main driver for moving from wafer to panel level packaging is of course lowering the packaging cost. More packages can be processed in parallel, and rectangular panel formats have a much better area utilization than circular wafers. With the advent of chiplet technology and the application to large body size packages e.g. HPC modules Panel Level Packaging is actually gaining momentum as an option for lower cost and high-density packaging. The PDC will give a status of the current Fan-in and Fanout Wafer Level Packaging as well as Panel Level Packaging. This will include material and process discussion, technologies, equipment, applications and market trends as well as cost and environmental aspects.

The PDC will give a status of the current Fan-in and Fan-out Wafer Level Packaging as well as Panel Level Packaging. This will include material and process discussion, technologies, equipment, applications and market trends as well as cost and environmental aspects.

## **Course Outline:**

- 1. Introduction to Advanced Packaging

- 2. Trends in Wafer Level Packaging

- 3. Fan-In and Fan-out Wafer Level: Material, Processes, Applications

- 4. Introduction and Definition Panel Level Packaging (PLP)

- 5. Fan-out Panel Level Packaging: Technologies, Challenges & Opportunities

## Who Should Attend:

Anyone who is interested in Advanced Packaging, Fan-in and Fan-out Wafer Level Packaging and the transition to Panel Level Packaging. Engineers and managers are welcome as detailed technology descriptions as well as market trends, applications and cost modelling are presented.

## 4. ELIMINATING FAILURE MECHANISMS IN ADVANCED PACKAGES

## Course Leader: Darvin Edwards – Edwards Enterprises

## **Course Description:**

Primary reliability failure mechanisms that plague semiconductor packages will be detailed along with solutions to enable faster qualification. The reliability of new package technologies such as heterogeneous package integration and chiplets will be emphasized, as well as an overview of reliability issues in more traditional packages. Topics highlighted include reliability of Direct Cu Bonding (DCB), high density interconnect (HDI) reliability, TSV-chip interactions, micro bump mechanical reliability, electromigration performance, stress induced interlevel dielectric (ILD) damage under bumps and Cu pillars, saw induced ILD damage, solder joint reliability, the impact of aging on reliability performance and many more. Primary failure analysis techniques will be described. For each failure mode, the resultant failure mechanisms and failure analysis techniques required to verify the mechanisms will be summarized. This solutions-focused course concentrates on the key process parameters, design techniques and material selections that can eliminate failures and improve reliability, ensuring participants can design-in reliability and design-out failures for quicker time to market. A primary goal is to give the student an intuitive understanding of the interaction between the various tradeoffs and to provide the knowledge of the methodologies and tools needed to drive early evaluation of these reliability risks.

## **Course Outline:**

- 1. Introduction to Package Reliability

- 2. Failure Modes vs. Failure Mechanisms

- 3. Failure Analysis Techniques

- 4. FC-BGA Package Failure Mechanisms

- 5. WLCSP Package Failure Mechanisms

- Embedded Die & Fan-Out WLP/PLP Failure Mechanisms

- 7. TSV Failure Mechanisms

- High Density Interconnection Reliability

Direct Bond Interconnect Reliability and

- Testing

- 10. Chiplet Challenges

- 11. Materials, Modeling, Design Rules and Reliability

- 12. Summary

## Who Should Attend:

This class is for all who work with IC packaging, package reliability, package development, package design, and package processing where a working knowledge of package failure mechanisms is beneficial. Beginning engineers and those skilled in the art will benefit from the holistic failure mechanism descriptions and the provided proven solutions.

## 5. INTRODUCTION TO AND ADVANCES IN 2.3D FAN-OUT WAFER LEVEL PACKAGING (FO-WLP)

## Course Leader: Beth Keser – Zero ASIC

## **Course Description:**

Fan-out wafer level packaging (FO-WLP) technologies have been developed across the industry over the past 20 years and have been in high volume manufacturing for over 16 years. FO-WLP has matured enough that it has come to a crossroads where it has the potential to change the electronic packaging industry by eliminating wirebond and bump interconnections, substrates, leadframes, and the traditional flip chip or wirebond chip attach and underfill assembly technologies across multiple applications. After scale-up and high-volume manufacture of simple single-chip Fan-Out Wafer Level Packaging (FO-WLP) solutions by companies like Qualcomm and Infineon, now many premier semiconductor companies and OEMs have adopted Advanced Fan-Out structures including Apple, AMD, MediaTek, and HiSilicon. These companies are leveraging foundry technologies like InFO offered by TSMC as well as OSAT solutions from ASE, Amkor, SPIL, PTI, and DECA.

The introductory portion of this course will cover the advantages of FO-WLP, potential application spaces; package structures available in the industry; materials, equipment and process challenges; and reliability. The advanced topics will cover potential application spaces, advanced package structures available in the industry, adopting 2.3D chips first and chips last fan-out technology for chiplets, technology roadmaps, and benchmarking.

## **Course Outline:**

- 1. Definitions and Advantages

- 2. Applications

- 3. Early Package Structures

- 4. Materials

- 5. Equipment

- 6. Design Rules and Reliability

- 7. Advanced Applications Including Chiplets

- 8. Package Structures Including Advanced FO Technologies

- 9. Technology Roadmap

- 10. Panel Challenges

- 11. Benchmarking

## Who Should Attend:

Engineers and managers responsible for advanced packaging development, package characterization, package quality, package reliability and package design should attend this course. Suppliers who are interested in supporting the materials and equipment supply chain should also attend. Both newcomers and experienced practitioners are welcome.

## 6. WAFER-TO-WAFER AND DIE-TO-WAFER HYBRID BONDING FOR ADVANCED INTERCONNECTS Course Leader: Viorel Dragoi – EV Group E. Thallner GmbH

## **Course Description:**

This course addresses fundamental and practical aspects of low temperature fusion and hybrid bonding, aiming to provide a good understanding of the current status and potential of this technology to provide manufacturing solutions for current and future applications. The course starts with a brief overview of all wafer bonding processes currently in use. A detailed explanation of the working principles of low temperature fusion and hybrid bonding is presented. Aspects related to material specifications and surface preparation are reviewed. Wafer-to-wafer alignment concepts are further introduced, with emphasis on face-to-face alignment. An overlay model is introduced and its benefits of its use are illustrated with experimental results. Aspects of implementing advanced process control methods are discussed, with an example on bond wave monitoring and control.

The concept of die-to-wafer bonding is introduced as a heterogeneous integration technology for chiplets-based applications. The different process flows available are reviewed. Some important aspects specific to die-to-wafer bonding are discussed, with emphasis on dies preparation and specific requirements of the various process flows. Experimental results are used for illustration of this technology's capabilities. This course concludes with a brief overview of the current and future challenges of wafer bonding.

- Introduction: Wafer Bonding Processes Short Overview (Principles, Basic Conditions)

- 2. Short Overview of the Wafer Bonding Process Variables

- 3. Low Temperature Fusion Bonding: Description, Specifications, Surface Preparation and Activation, Bonding Process

- 4. Low Temperature Hybrid Bonding: Description, Specifications, Surface Preparation, Bonding Process

- 5. Wafer-to-wafer Alignment: General Principles (Methods, Errors), SmartView Alignment Introduction, Overlay and Distortion

- 6. Advanced Process Control: Using Numerical Simulation and Data Analysis

- 7. Advanced Bond Wave Monitoring and Control

- 8. Short Overview of Wafer Bonding -Specific Metrology: Defects, Bond Strength

- 9. Die-to-wafer Bonding: Introduction of the Concept and Process Flows

- 10. Die-to-wafer: Specific Process Features Compared to Wafer-to-wafer Bonding (Dies Preparation, Alignment, and Metrology)

- 11. Summary: Short Overview of Wafer Bonding Current and Future Challenges

The course is addressed to engineers involved in heterogeneous integration technology development who are willing to understand the status of wafer bonding technology and its applications potential. Principles and concepts are presented and explained together with more advanced topics. No prior experience in wafer-to-wafer or die-to-wafer bonding is required.

## 7. FUNDAMENTALS OF FABRICATION PROCESSES AND RF DESIGN OF ADVANCED PACKAGES INCLUDING FAN-OUT, CHIPLETS, GLASS AND POLYMER INTERPOSER

Course Leaders: Ivan Ndip – Brandenburg University of Technology/Fraunhofer IZM and Markus Wöhrmann – Fraunhofer IZM

## **Course Description:**

Advanced packaging technologies such as fanout wafer and panel level packages (FO-WLPs, FO-PLPs), interposers (e.g., glass interposers with TGVs, polymer interposers) and chipembedding packages (e.g., PCB embedding) play a key role in heterogeneous integration and enable the development of system in package (SiP) modules, antenna in/on-package (AiP/AoP) and chiplet based systems. The packaging materials, fabrication processes and RF performance of these packages contribute significantly to the cost, performance and reliability of the entire system.

The main objective of this course is to provide a thorough overview of packaging materials, fundamentals of fabrication processes and basic RF design of advanced packages (e.g., FO-WLPs, FO-PLPs, glass and polymer interposers, SiP and AiP/AoP) for a wide range of applications. Furthermore, an introduction to chiplet design and heterogeneous integration, considering interconnects for chiplet communication and UCle, will be given. The applications driving advanced packages such 5G, 6G communication, radar sensing, high-performance computing (HPC) and Al in various industries will also be extensively discussed.

## **Course Outline:**

Introduction, Basic Definitions and Explanations of Key Terminologies Related to Advanced Packages, RF Design, Chiplets, and Heterogeneous Integration

- 2. Applications Driving Advanced Packages such as 5G, 6G Communication, Radar Sensing, HPC, and AI in Various Industries

- 3. Overview of Different Types of Advanced Packages, Current Trends, and Future Directions

- 4. Challenges and Key Requirements of Advanced Packages for RF Applications

- 5. Fundamentals of Packaging Materials and Fabrication Processes of FO-WLPs/ FO-PLPs, Interposers (Glass, Organic), and AiP/AoP

- Role of Electrical Parameters (Dk and Df) of Materials in RF Packaging and Methods for Measurement-Based Extraction of Dk and Df of Different Packaging Materials

- 7. Fundamentals of RF Design of Building Blocks of FO-WLPs/FO-PLPs, Interposers (Glass, Organic), and AiP/AoP

- 8. Introduction to Chiplet Design and Heterogeneous Integration, Considering Interconnects for Lateral Chiplet Communication and UCle

- 9. Examples of Advanced Packages Fabricated at Fraunhofer IZM

## Who Should Attend:

Engineers, scientists, researchers, designers, managers, and graduate students interested in the fundamentals of electronic packaging as well as those involved in the process of electrical design, layout, processing, fabrication, and/or system-integration of electronic packages for emerging applications (e.g., 5G, 6G, mmWave radar sensors) should attend.

## 8. DESIGN OF RELIABLE DATA CENTER COOLING SYSTEMS Course Leaders: Patrick McCluskey and Damena Agonafer – University of Maryland

## **Course Description:**

Power electronics are becoming ubiquitous in engineered systems as they replace traditional ways to control the generation, distribution, and use of energy. They are used in products as diverse as home appliances, cell phone towers, aircraft, wind turbines, radar systems, smart grids, and data centers. This widespread incorporation has resulted in significant improvements in efficiency over previous technologies, but it also has made it essential that the reliability of power electronics be characterized and enhanced. Recently, increased power levels, made possible by new compound semiconductor materials, combined with increased packaging density have led to higher heat densities in power electronic systems, especially inside the switching module, making thermal management more critical to performance and reliability of power electronics. This course will emphasize approaches to integrated thermal packaging that address performance limits and reliability

concerns associated with increased power levels and power density. Following a quick review of active heat transfer techniques, along with prognostic health management, this short course will present the latest developments in the materials (e.g. organic, flexible), packaging, assembly, and thermal management of power electronic modules, MEMS, and systems and in the techniques for their reliability assessment.

## **Course Outline:**

- 1. State of the Art Data Center Cooling

- 2. Single Phase Liquid and Hybrid Cooling Approaches

- 3. Thermal Modeling

- 4. Reliability and Availability Modeling

- 5. Software Tools for Modeling

- 6. Examples of Leading-Edge Cooling Solutions

## Who Should Attend:

Data Center Designers, HVAC Engineers, Electronic Packaging Engineers and Managers interested in addressing key challenges to the growth of data centers.

## AFTERNOON COURSES 1:30 p.m. – 5:30 p.m.

## 9. 3D PACKAGING FAILURE ANALYSIS – FAILURE MECHANISMS AND ANALYTICAL TOOLS Course Leader: Deepak Goyal – Independent Consultant

## **Course Description:**

Heterogeneous Integration (HI) of disparate computing and communications functions is a key enabler of performance in microelectronic systems. HI is crucially enabled by advanced packaging since packages are an optimal HI platform. This technical course will provide an overview of the failure modes and mechanisms observed in 2.5D/3D packages. A brief introduction to the methodology of failure analysis of these packages will be described. The focus of the course will be on package failure mechanisms highlighted by case studies and on analytical tools and techniques currently used and the future direction for the tools and techniques required for successful and timely failure analysis of 3D package technologies. A discussion on the strategies for use of these techniques and a flow chart for failure analysis will be included.

- 1. 2.5D/3D Package Technology Trends, Drivers & Challenges

- 2. Failure Analysis Challenges Offered by 3D Package Technology Roadmap

- 3. Introduction to the Methodology of Failure Analysis of 3D Packages

- 4. Current Analytical Capabilities for Package Fault Isolation and Failure Analysis

- Strategies to Use These Techniques to Identify Failures and Understand Failure Mechanisms

- 6. Analytical Capabilities to Support Next Generation 3D Packaging Technologies

- 7. Typical Failure Analysis Flow Charts for Opens and Shorts.

- Failure Modes/mechanisms Including Chip/package Interactions, 1st/2nd Level Interconnections and Package/board Substrates.

- 9. Failure Analysis Case Studies.

Engineers and technical managers who are involved in package technology development, assembly manufacturing, reliability assessment of packages and failure analysis will benefit from this course.

## 10. DIAMOND FOR HETEROGENEOUS INTEGRATION

## Course Leader: Joana Mendes – University of Aveiro

## **Course Description:**

Enhanced power density in 3D/2.5D integrated systems has led to a significant increase in the complexity of thermal management. In fact, thermal issues systems are increasingly moving to the forefront as a major challenge limiting the overall electrical performance and reliability of components in 3D/2.5D integrated systems. The thermal integrity of future heterogeneously integrated systems will not be achieved unless problems related to material properties are addressed. This course will discuss the potential of integrating synthetic diamond in complex SiPs to improve heat extraction and increase reliability. The methods for fabricating synthetic diamonds will be described and their pros and cons discussed. Different strategies that can be employed to integrate diamond in the concept of 3D/2.5D integration will be proposed and a critical assessment of the expected technical challenges and possible solutions will be made. Recent research work and breakthroughs from both industry and academia will be presented. Finally, the recent trend of gemstone market saturation and the impact on the cost of synthetic diamond will be discussed. NOTE: a video of a much-shorter version or segment is available on IEEE.tv (https://r6.ieee.org/scveps/?p=3189)

## **Course Outline:**

- 1. Potential of Synthetic Diamond for Thermal Management Applications

- 2. Methods for Fabricating Synthetic Diamond, Advantages and Limitations

- 3. Integrating Synthetic Diamond at Different Levels in a SiP

- 4. Diamond for Thermal Management: Successful Examples

- 5. GaN HEMTS: Diamond Substrates and Diamond Capping

- 6. Semiconductor Disk Lasers: Diamond Submounts and Heat Spreaders

- 7. High Power Components: Diamond Boards and Die-carriers

- 8. Bonding of Diamond and Non-diamond Wafers

- 9. Microfluidics Using Diamond

- 10. Current Issues and Guidelines for Solutions

- 11. Foreseen Synthetic Diamond Market Trends

## Who Should Attend:

Researchers and practitioners looking for thermal management solutions for heterogeneously integrated packaging should attend. Managers considering the use of alternative approaches to thermal problems will also benefit from attending.

## 11. CHIPLET, HETEROGENEOUS INTEGRATION, AND CO-PACKAGED OPTICS

Course Leader: John Lau – Unimicron

## **Course Description:**

Chiplet is a chip design method and heterogeneous integration (HI) is a chip packaging method. HI uses packaging technology to integrate dissimilar chips, photonic devices, and/or components with different sizes and functions, and from different fabless design houses and foundries into a system or subsystem on a common package substrate. Co-packaged optics (CPO) are heterogeneous integration of the optical engine which consists of photonic ICs (PIC) and the electrical engine (EE) which consists of the electronic ICs (EIC) as well as the switch ASIC (application-specific integrated circuitry). The advantages of CPO are: (a) to reduce the length of the electrical interface between the OE/EE (or PIC/EIC) and the ASIC, (b) to reduce the energy required to drive the signal, and (c) to cut the latency which leads to better electrical performance. For the next few years, we will see more implementations of a higher level of chiplet designs and HI packaging and CPO, whether it is for cost, time-tomarket, performance, form factor, or power consumption. In this lecture, the introduction, recent advances, and trends in chiplet, HI, and CPO will be presented.

## **Course Outline:**

- 1. System on Chip (SOC)

- 2. The Origin of Chiplets

- 3. Chiplet Design and HI Packaging (1. Partition, 2. Split)

- 4. Communication Between Chiplets (EMIB, UCle, Bridge Embedded in Fan-Out EMC)

- 5. Chiplet Design and HI Packaging Multiple System and HI

- 6. Potential R&D Topics in Chiplet Design and HI Packaging

- 7. Trends in Chiplet Design and HI Packaging

- 8. Silicon Photonic

- 9. Data Centers and Optical Transceivers

- 10. Optical Engine (OE) and Electrical Engine (EE)

- 11. OBO (On-Board Optics), NBO (Near-Board Optics), and CPO (Co-Packaged Optics)

- 12. 3D HI of PIC and EIC

- 13. 3D HI of ASIC Switch, PIC and EIC w/o Bridges

- 14. 3D HI of GPU, HBM, Switch, PIC, EIC (Driven by AI)

- 15. HI of ASIC Switch, PIC and EIC on Glass Substrate

- 16. Potential R&D Topics and Trends in Co-Packaged Optics

## Who Should Attend:

If you (students, engineers, and managers) are involved with any aspect of the electronics industry, you should attend this course. It is equally suited for R&D professionals and scientists. Each attendee will receive more than 300 pages of lecture notes.

## 12. ANALYSIS OF FRACTURE AND DELAMINATION IN MICROELECTRONIC PACKAGES Course Leader: Andrew Tay – National University of Singapore

## **Course Description:**

The main objective of this course is to provide a fundamental understanding as well as proven techniques of applying the fracture mechanics methodology to predicting fracture and delamination in microelectronic packages. The mechanism of popcorn cracking failure will be described and analyzed. Simulation of heat transfer and moisture diffusion processes occurring during package gualification and reflow will be described. An introduction to the fundamentals of interfacial fracture mechanics will be given together with descriptions of some numerical methods for calculating fracture mechanics parameters. Experiments which verify the methodology for predicting delamination in packages will be described followed by some case studies.

- 1. Hygrothermal Stresses in Microelectronics Packages

- 2. Finite Element Analysis and Stress Singularities

- 3. Fundamentals of Fracture Mechanics Methodology

- 4. Determination of Fracture Mechanics Parameters

- 5. Measurement of Fracture Toughness

- 6. Experimental Verification of the Fracture Mechanics Methodology

- Case Studies on Delamination of Padencapsulant Interfaces, Die-attach Layers and On-chip Interconnect Structures (BEOL)

- 8. Cohesive Zone Modelling of Delamination and Case Studies

This course is designed for packaging design engineers who perform reliability analysis of microelectronics and photonics packages. Knowledge of finite element analysis is an advantage but not essential.

### 13. ADVANCED FAN-OUT DEVELOPMENTS AND APPLICATIONS

Course Leaders: John Hunt and Jan Vardaman – TechSearch International, Inc.

## **Course Description:**

Fan-out wafer-level packaging (FO-WLP) has evolved from a low-cost packaging option for automotive and mobile applications to a highperformance computing packaging solution. Both chip-first and chip-last solutions have been adopted and are expanding in complexity to serve a range of applications including AI training and inferencing, replacing silicon with an organic redistribution layer (RDL) as the interposer. The potential for packaging for RF and photonics is also described. The course provides a brief overview of the various fan-out packages, a history of their evolution, and discussion of the current structures and reasons for adoption in each application. Differences between the three basic processes flows: Chip First Die Down, Chip First Die Up, and Chip Last are explained with examples of each structure. Bridge solutions are described, including process flows, advantages, and applications. The course also discusses the move to large panels for cost-reduction and discusses both the potential advantages and challenges. Production examples and process flows are included.

## **Course Outline:**

- 1. Overview: Drivers for Fan Out

- 2. Basic Low-density Fan Out

- 3. 3D Fan Out Structures

- 4. High Density Die to Die Fan Out

- 5. Fan Out Embedded Bridge Technology

- 6. Fan Out System in Package

- 7. Antenna in Package

- 8. Fan Out Silicon Photonics Integration

- 9. Fan Out Memory Packaging