# Heterogeneous Integration at DARPA: Pathfinding and Progress in Assembly Approaches

### **Daniel S. Green**

U.S. Defense Advanced Research Projects Agency (DARPA) Arlington, VA (now with Office of Naval Research, Arlington, VA)

Presented by Jeffrey C. Demmin, Booz Allen Hamilton 68<sup>th</sup> IEEE Electronic Components and Technology Conference

29 May 2018

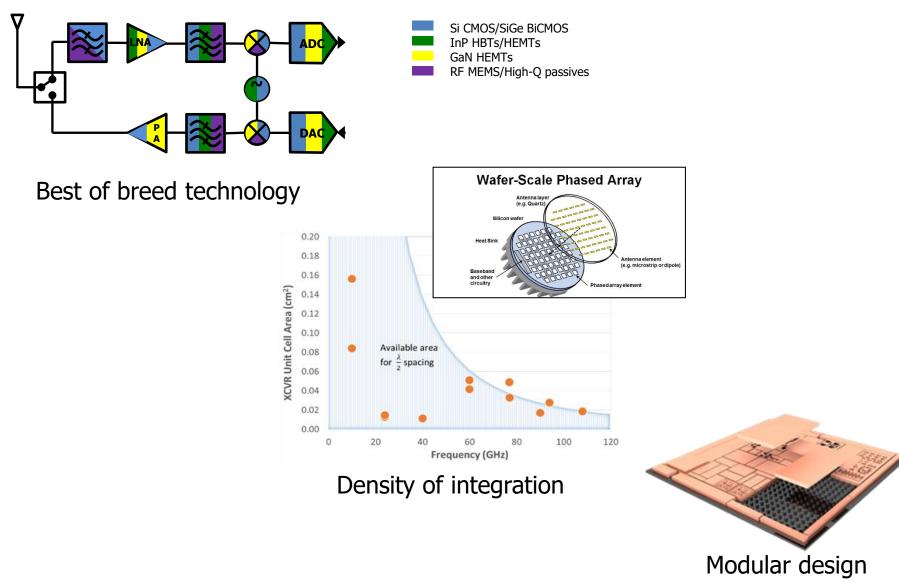

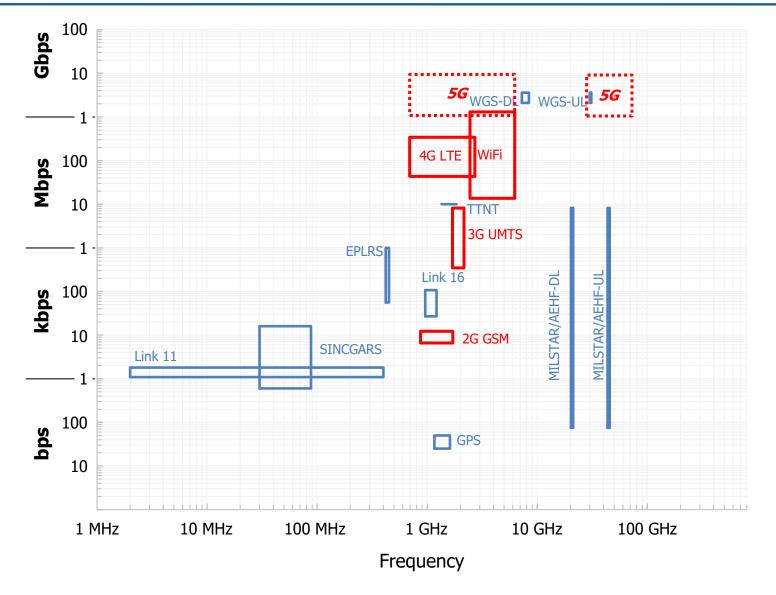

# Why Heterogeneous Integration?

# Civilian and defense needs overlap at the leading edge

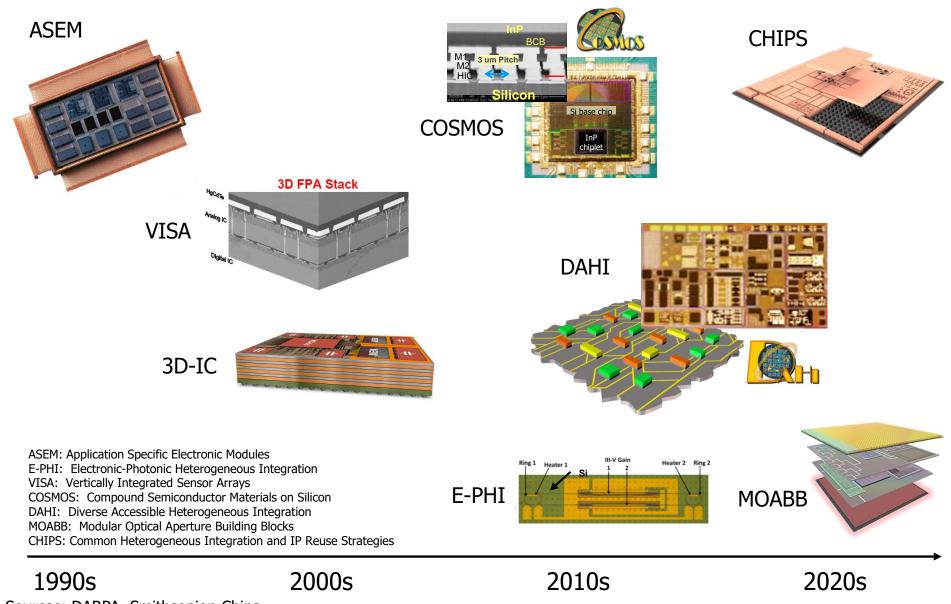

# DARPA's long history of innovation in integration

Sources: DARPA, Smithsonion Chips Distribution Statement "A" (Approved for Public Release, Distribution Unlimited)

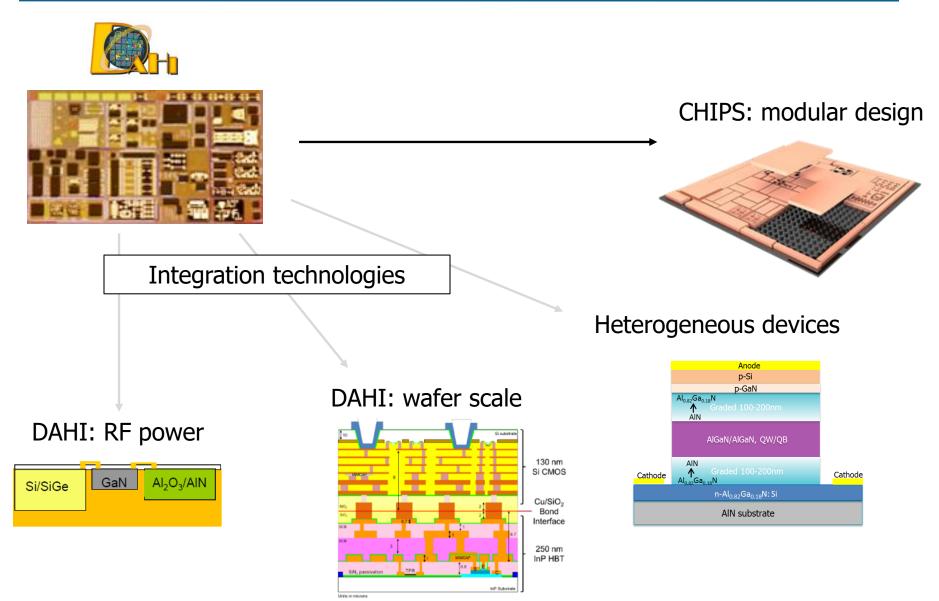

# **DARPA** What is heterogeneous integration?

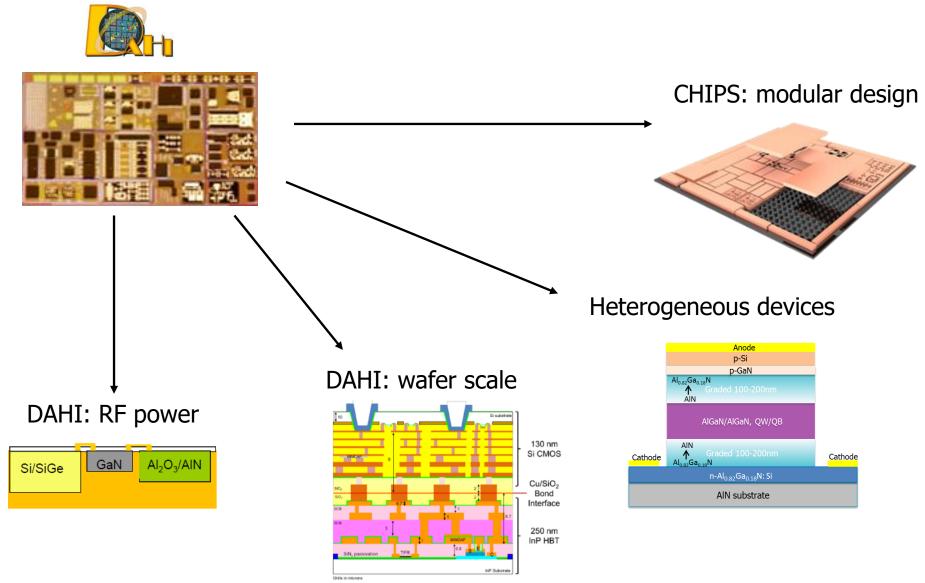

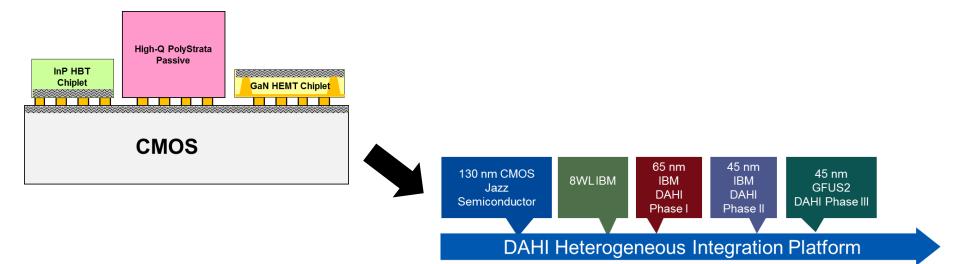

# DARPA's DAHI program: Diverse Accessible Heterogeneous Integration

### **Picture of MPW0 Reticle**

### **Picture of MPW1 Reticle**

#

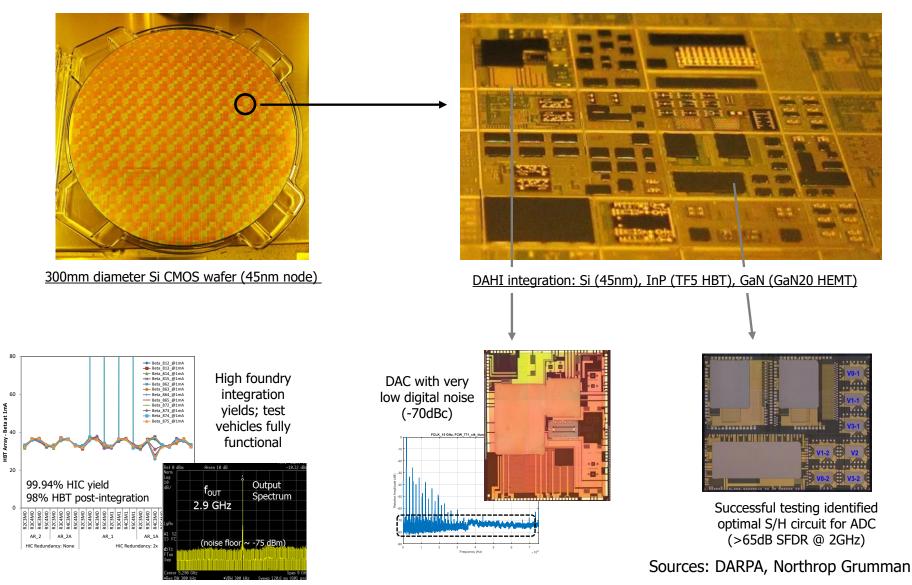

### MPW3 in Fab

### Sources: DARPA, Northrop Grumman

| Technology                       | MPW0           | MPW1                        | MPW2                        | MPW3                     | Future MPWs                 |

|----------------------------------|----------------|-----------------------------|-----------------------------|--------------------------|-----------------------------|

| CMOS                             | IBM 65nm       | GF 45 nm                    | GF 45 nm                    | GF 45 nm                 | GF 45 nm                    |

| InP HBT                          | TF4 (2 metals) | TF4 (3 metals)              | TF4 (4 metals)              | TF4 (4 metals)           | TF4 (4 metals)              |

|                                  |                | TF5 (3 metals)              | TF5 (4 metals)              | TF5 (4 metals)           | TF5 (4 metals)              |

| InP Varactor<br>Diode            |                |                             |                             |                          | AD1                         |

| GaN HEMT                         | GaN20          | GaN20                       | GaN20                       | GaN20                    | GaN20                       |

|                                  | T3 (HRL)       | T3 (HRL)                    | T3 (HRL)                    | T3 (HRL)                 | T3 (HRL)                    |

| GaAs HEMT                        |                |                             |                             | Р3К6                     | P3K6                        |

| Passive<br>Components            |                | PolyStrata<br>(Nuvotronics) | PolyStrata<br>(Nuvotronics) | PolyStrata (Nuvotronics) | PolyStrata<br>(Nuvotronics) |

| Base<br>Substrate                | CMOS           | CMOS                        | CMOS                        | CMOS                     | CMOS                        |

|                                  |                |                             |                             | SiC Interposer (IWP5)    | SiC Interposer (IWP5)       |

| NP HET<br>Capet<br>Capet<br>CMOS |                |                             |                             | In fab                   |                             |

Sources: DARPA, Northrop Grumman

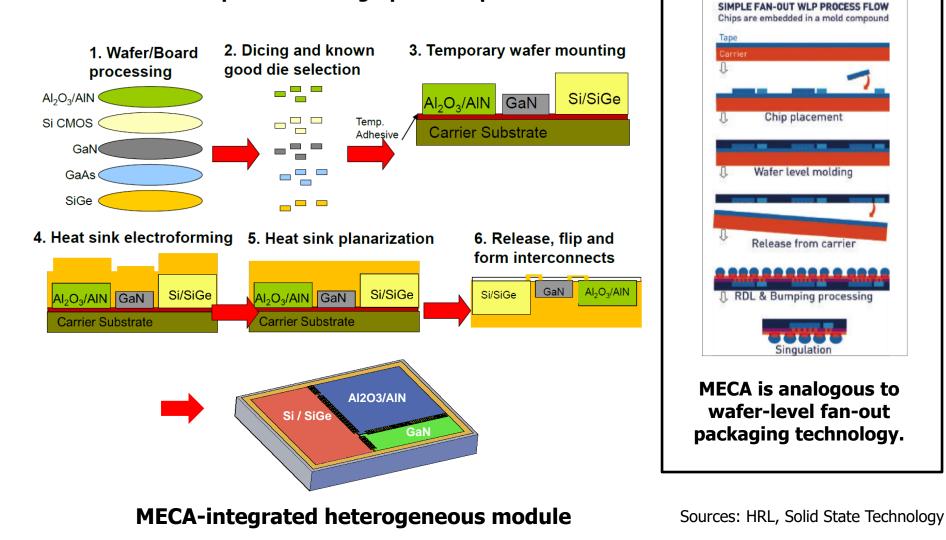

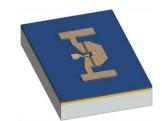

# MECA enables heterogeneous integration with a metal interconnect platform for high-power requirements.

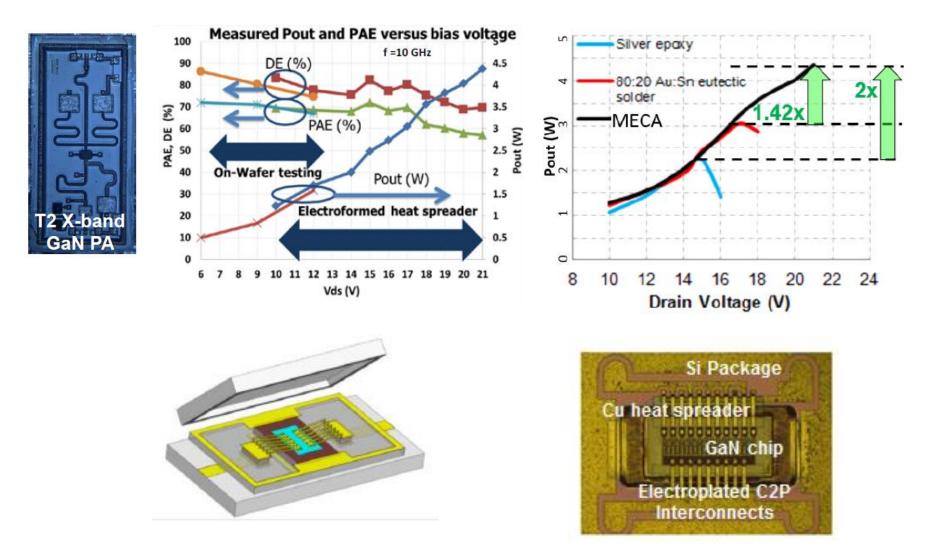

### Integration in electroformed heat spreader: 1.4-2x improvement in PA performance

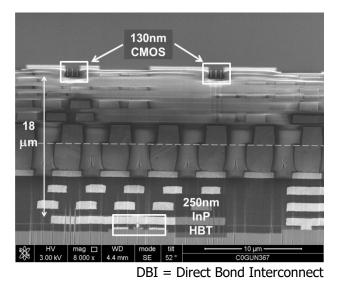

### Heterogeneous integration for mm-wave: Phased array beamformers

- Can maintain  $\lambda/2$  channel spacing as frequencies increase

- CMOS control circuitry closely integrated with RF chain

- Improved channel performance and efficiency with addition of III-V devices

- Fully integrated beamformer channels demonstrated with integrated InP devices and Si control electronics

- >100mW Pout Tx channel, 4.5 dB NF Rx

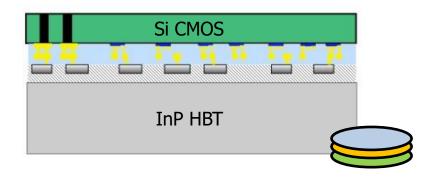

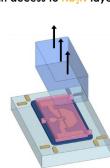

### Wafer-level heterogeneous integration

# 10 Sisubstrate 130 nm Sicketrate 130 nm Sicketrate Sicketrate

### **InP/CMOS** with DBI Process

### **Integration schematic**

### Source: Teledyne

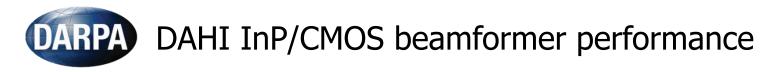

### **Q-band InP/CMOS Tx Channel Layout**

Channel dimensions: 3.0x0.6mm<sup>2</sup>

### **Q-band Tx Channel**

- 57 HBTs, 1704 CMOS gates, 76 HICs

- Pdiss  $\sim 1W$

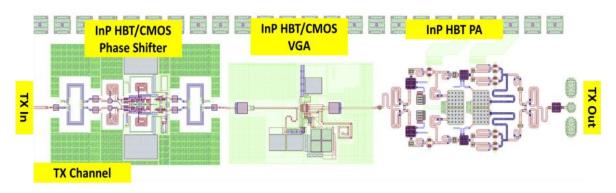

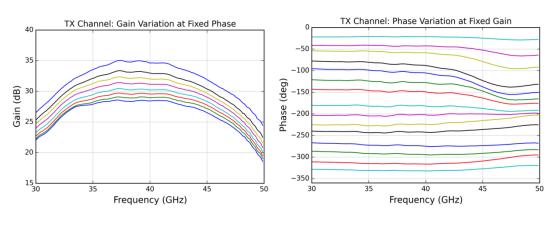

- 28-35 dB gain variation

- $5^{\circ}$  RMS phase error at 40 GHz

- 20.3 dBm Psat, 18.1 dBm P1dB

### **Measured Gain and Phase Variation**

### **Measured Tx Channel Power**

### Source: Teledyne

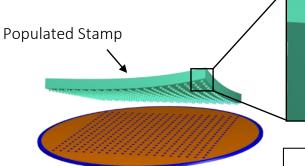

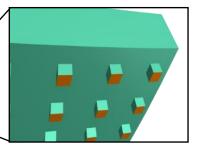

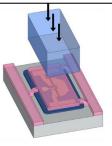

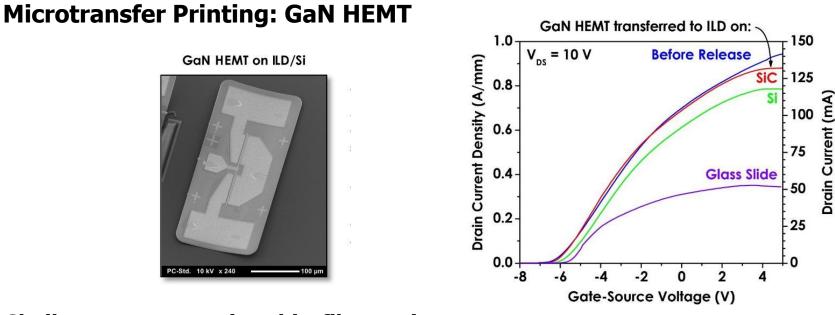

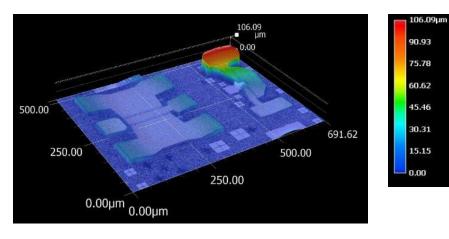

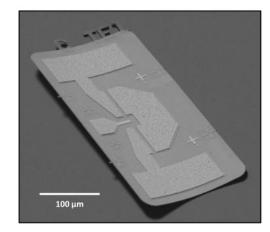

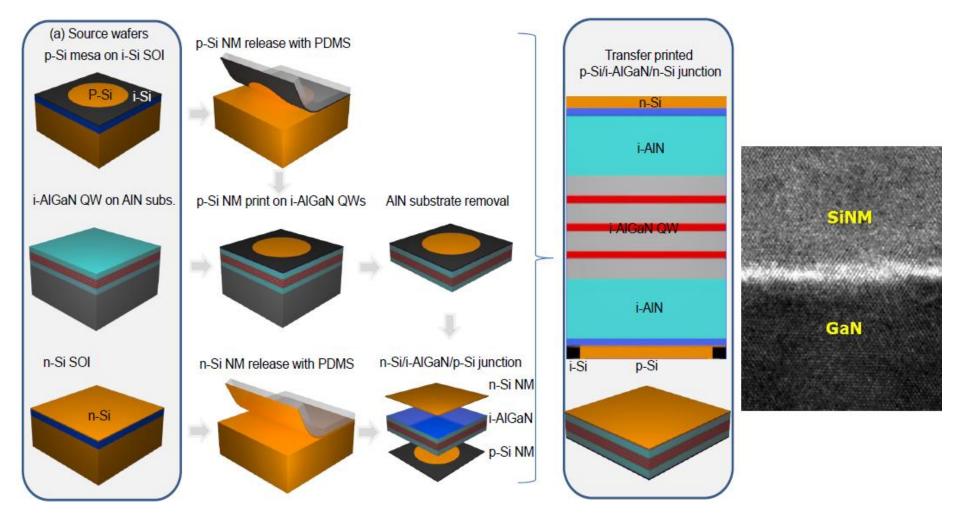

# **Microtransfer Printing**

Fabricate GaN devices on Nb<sub>2</sub>N template on SiC substrate using standard fabrication processes.

2. Mask known-good GaN devices for transfer and recess etch to gain access to Nb<sub>2</sub>N layer.

5. Release GaN device from polymer stamp.

Pattern photoresist anchors and protective mask.

Selectively etch Nb<sub>2</sub>N layer using XeF<sub>2</sub> reactive gas.

Remove photoresist protective mask from transferred GaN device.

4. Transfer print GaN device to

target substrate using polymer

stamp and optional adhesive.

### Challenges to managing thin-film strain

### Source: Naval Research Laboratory

### Transfer printing can stack nano-membrane layers to create junctions and devices

Sources: U. of Wisconsin, Michigan State U.

Common Heterogeneous Integration and IP Reuse Strategies: The next step in heterogeneous integration

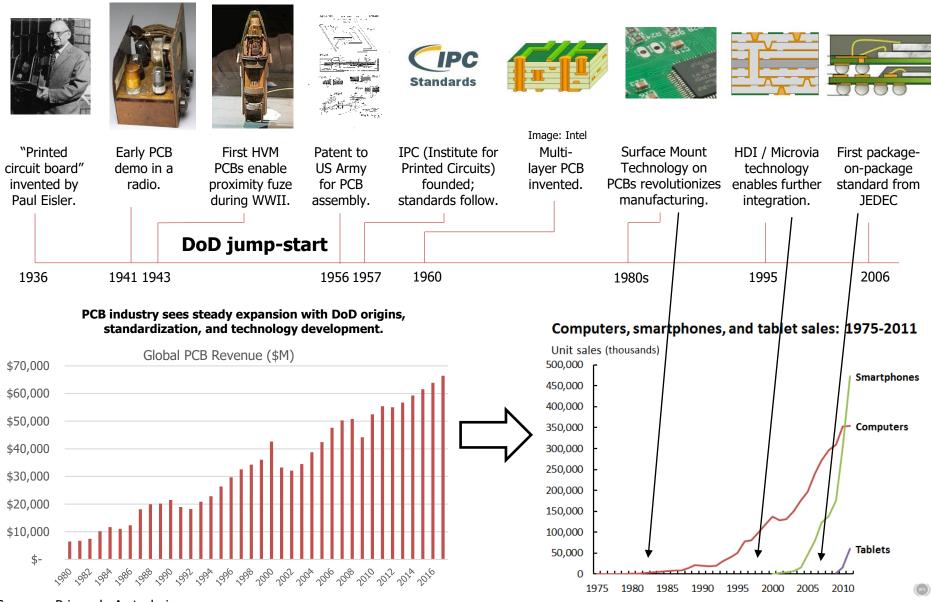

# **DARPA** Integration impact driven by **Standards** and **Modularity**

Sources: Prismark, Arstechnica, USPTO, Wikipedia, IPC, SMTA

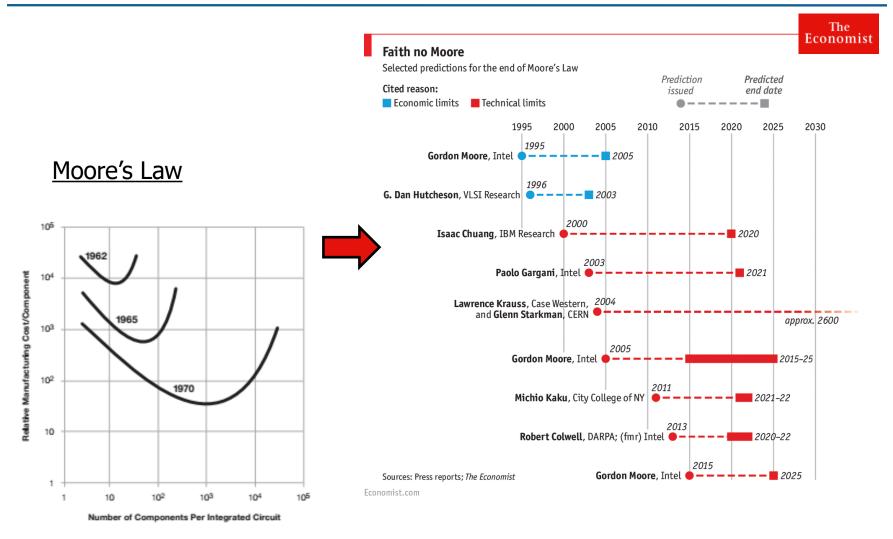

# End of Moore's Law?

# Changes in silicon industry will be felt by compound semiconductors

Source: Electronics Magazine, Economist.com

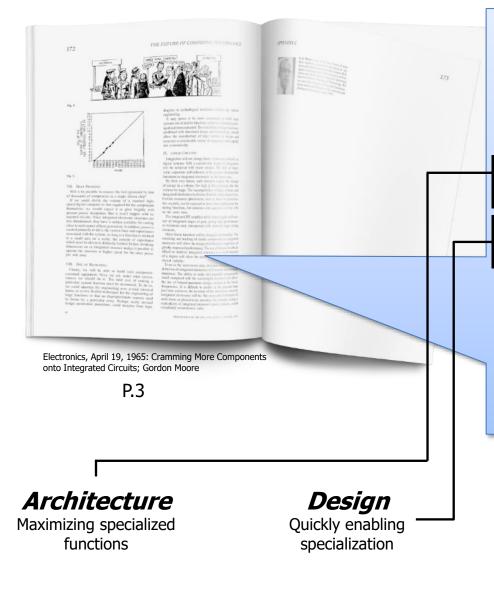

It may prove to be more economical to build large systems out of smaller functions, which are separately packaged and interconnected. The availability of large functions, combined with functional design and construction, should allow the manufacturer of large systems to design and construct a considerable variety of equipment both rapidly and economically.

### The experts look ahead

### Cramming more components onto integrated circuits

With unit cost falling as the number of components per circuit rises, by 1975 economics may dictate equeezing as many as 65,000 components on a single silicon chip

By Gordon E. Moore Dructur, Research and Development Laboratories, Pair-Still Randoorelanter ribial set of Patienhild Cartana and Instrument Corp.

The latent of integrated electronics, is the inner of electronus thef. The abandops of integration will bring shoul a wildling, the improved reliability much pushlo proliferation of decocories, penhargible science into many HOW WITH Integrated cleants will lead to such worders to here:

lower costs and with lister larn-around. compatens-or at loss trensingly swince tot to a central com-Present and Makes page-automatic controls for entereoffiles, and personal possible communication equipment. The electronic writeauthority which are referred to as microeleen wards needs only a doplay to be liquidite today.

But the biggest potential lies in the production of lance ann. In temphone communications, imagined circult in digital fibers will asparate charate is on makipies aquipment. Integrated circuits will also awitch winghous circuits and perform data proceeding.

Computers will be recorporateful, and will be organized in completely different ways. For example, memories hailt of integrated electronics may be distributed throughout the

### The extra a

The antible Dr. Continue F. Morras is non- of the new time of attackments in applicates, colorado in the physical solutions where them is decret which, the aerosed a B.J. decret in characteristic from the decret which are the second of a B.J. decret in characteristic from the decret which are the fulfillential in applicate of Technology has seen one of the transmission of fulfille Marine and has been directive of the second or the second of the second of the second of the second of the decret of the second of the second of the decret of the second of the second of the second of the decret of the second of the second of the second of the decret of the second of the s instant of the sec

Electronics, Volume 38, Humber 8, April 18, 1955

100

mathine instead of heing conservated in a

circuits will allow the construction of larger pr

Machines shed for in these in existence index.

well as any additional ones that result in e its

eligits were first investigated is the late 15

less was to miniaturize electronics e arises en

mutingly complex electronic functions in line

stersenarship techniques for inclusional con

(Tim structures and semicondector talgested of

Each approach evolved rapidly and conve such borrowed ischolgess from another. Many

The advocates of services ductor integra

ballane the way of the famous to be a combinant

a beady using the improved characteristics of it

tion by applying such films directly to association for substants. These advantating a technolog

films are developing applications discharges, meet of active presidential are devices to the p

Both approaches have staviard until

minimum weight. Several approaches evol-

tions matelied to the user as irriducible units

trouis, I recar all th

By integrated ch

our approaches.

in equipment to by

G. E. Moore is one of the new breed of electronic engineers, schooled in the physical sciences rather than in electronics. He earned a B.S. degree in chemistry from the University of California and a Ph.D. degree in physical chemistry from the California Institute of Technology. He was one of the founders of Fairchild Semiconductor and has been Director of the research and development laboratories since 1959

### The establishment

becaused electronics is a stablished using. In techniquest abuest mondatory for resventitary systems, since the rehald fey, size and weight required by some of them is addressable only with integration. Such programs as Aprille, for manual more flight, have demonstrated the reliability of laregressed electronics by showing that complete classic fine-tions are as free from failure as the best individual maske-Milercompative in the commercial company field have

stachtion in design or in carly production employing ima-grated abschools. These machines cost less and perform hater than these which use "conventional" electronics. instruments of variant sorts, especially the tupicly incrassing members corploying digital tachs income are starting an interaction because it can see in both manufacture

and design. The use of linear integrated circuity is still restricted. primarily to the military. Such imagrated functions are noperceive and net available in the variety regained to satisfy a major function of linear electronics. But the first applica-

### tion are beginning to appear incommercial electronics, par-ticularly in optigment which reach law-droparcey amplifien of small slop Rationality counts

In almost every case, integrated a technology has denote strated high reliability. Doos at the prosent level of product tion -- law compared to that of discrete components -- it offor related synthetic out, and in many systems improved performance has been realized.

Integrated electronics will make electronic techniques more generally available throughout all of society, perform ing more functions that present is are done inadequately by other techniques or not done at a l. The principal advantages will be lower unvis and greatly simplified design-payoffs from a mush rapply of low-cost functional packages Formost applications, som konstactor integrated circuits.

will predominate. Semicorductor devices are the only mocouble candidates presently in avidence for the active ele-ments of traggrand circuits. Pour te senicorductor elements look attractive too, because of their potential flar low-cost and high reliability, but they can be used on ly if propiation is not a prices togainty. Silicon is likely to remain the basic material, although

afters will be of me in specific applications. For example, pill an anenide will be important in integrated encourses Englises. But silicon will predominate it lower fromencies because of the technology which has abrach evolved around it and its oracle, and because it is an abundant and relationly interpretative starting meterial.

### Costs and curves

Reduced cost is one of the big stituctures of integrated electronics, and the cost advantage continues to increase or the technology evolves toward the production of larger and functions on a single service statute to explanate larger circuit For simple a sould, the cost per component is usually investely. propertional to the merilest of components, the musit of the

Electronics, Volume 38, Number 5, April 10, 1963

equivalent piece of sensionche up to the equivalent packap containing more composeries. But as composeries are added decreased yields more than compensate for the in complexity, tending to mise the cost per comp derrise ministers cost at my given there is the e-

the industriegy. At present, it is reached when 5 rents are used per strout. But the maximum tarts while the entire cost corners latting one prightle is took sheed five years, a plot of costs suggests that recently and net companyed recently be exceeded in an

about 1,000 components per circuit (providing o fanctions on he endaged in recibrate most day. the manufacturing cost per component can be a carls a tanih of the present and, The complexity for minimum compressed

counsed at a usic of rangity a Gatar of two per graph on wet page). Cartainly over the shortte can be expected to continue, if set to increase former term, the taxe of increase is a bit more tax though there is no issues to believe it will not rear contant for at loss 10 years. That means by 1973 ber of components per subgrated circuit for many with with the

I believe that such a large cleanit survive built and a

With the dimensional tubescore sites dy being sugarand circuits, in slated high-pertile can be built on content two thermaniths of an inch of

igner: with On the allows water parents used, usual b as lock or more in diameter, deve to angle some for such a structure if the components can be alrawely picked with no space wisked In the second seco where a level of complexity above the presents available megaled crimits are already underway using multilator anations make such array meta-batics patients around by defects files. Xash a density of components can be achieved by preparat optical techniques and does not require the more exats; bedreapues, such as electron beam operations, which are being tracked to stable over resulter thracherer.

### increasing the yield.

There is no functioneral obtainty to achieving deniar pields of 100%. All present, packaging costs to far exceed The post of the sensional active deviations should that there is no incentive to improve yields, but they can be mained as high as

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

Flactonics Ve

extremely loss there was lach incruitive. Today ordinary toregrated a loads are must with stable comparable with those pation will make larger as communed, if other toroid i desirable

### Field peoblem Will here reasolities neve the here generated by us

of thousands of composition in a single allocorchip. If we could strink the volume of a standard high-speed pial compare to that equival for the components thandigital company to that alves, no would expect to glow bright is with present perver distribution of the second sec of kest paramition. It as filling, power is mediad primarily in drive the vertices lines a openitances as sociated with the besteen. As long as a function is conflued to a small area of a warler, the answer of scitance which man be driven it distinctly findiged. In fair, shrinking climentations on an integrated structure caules i prosible to openie the separate at higher speed for the same power per unit ansa.

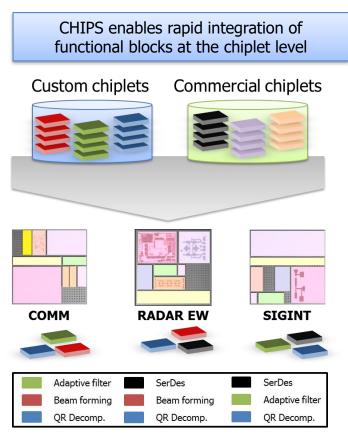

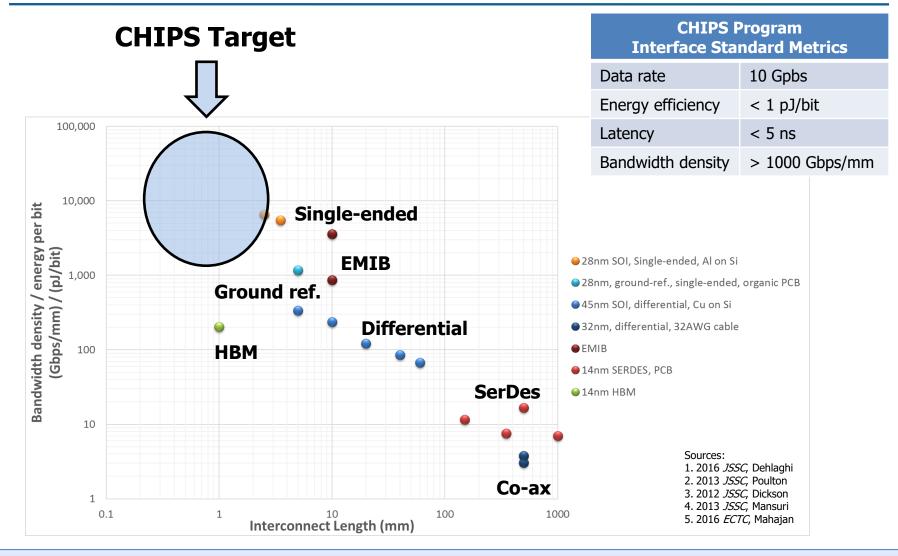

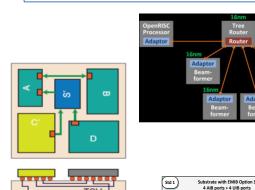

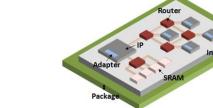

# What is CHIPS?

**CHIPS** will develop design tools, integration standards, and IP blocks required to demonstrate modular electronic systems that can leverage the best of DoD and commercial designs and technology.

### Today – Monolithic Tomorrow – Modular

CHIPS interface is one of many possible routes for efficient interdie communications

# CHIPS program: structure and timing

| PHASE 1                                                            | PH                           | ASE 2                   | PHASE 3              |                                               |  |

|--------------------------------------------------------------------|------------------------------|-------------------------|----------------------|-----------------------------------------------|--|

| Interface and IP Block Demo                                        | Module Demo                  | o with IP Blocks        | Rapid Module Upgrade |                                               |  |

| Integration platform Interface demo                                | Full system IP<br>reuse demo |                         | Reconfigured demo    |                                               |  |

| Phase 1a<br>(8 mo.) Phase 1b<br>(10 mo.)<br>Interface standards In | Ph                           | Phase 2 (18 mo.)        |                      | Phase 3 (12 mo.)<br>Module demo Rapid upgrade |  |

|                                                                    |                              | Modular Digital Systems |                      |                                               |  |

|                                                                    |                              | <b>1</b>                |                      |                                               |  |

|                                                                    |                              | Supporting Technologies |                      |                                               |  |

|                                                                    |                              | Į.                      |                      |                                               |  |

|                                                                    |                              | 2 Modular Analo         | g Systems            |                                               |  |

# Seeking CHIPS collaboration to help drive a common interface

Source: DARPA

# **DARPA** CHIPS: August 2017 Kickoff

Curve & RSA

# **CHIPS Team**

- Boeing

- Intel

Designs

Chiplets

ools

- Lockheed Martin

- Northrop Grumman

- Univ. of Michigan

- Intrinsix

- Jariet

- Micron

- North Carolina State

- Synopsys

- Cadence

- Georgia Tech

### CHIPS Approach Modularity Standards

Stratix 10 FPGA die

PRNG

Images sources: Lockheed Martin, Boeing, Intel, Intrinsix, Univ. of Michigan, 3GPP.org 23

# What's next?

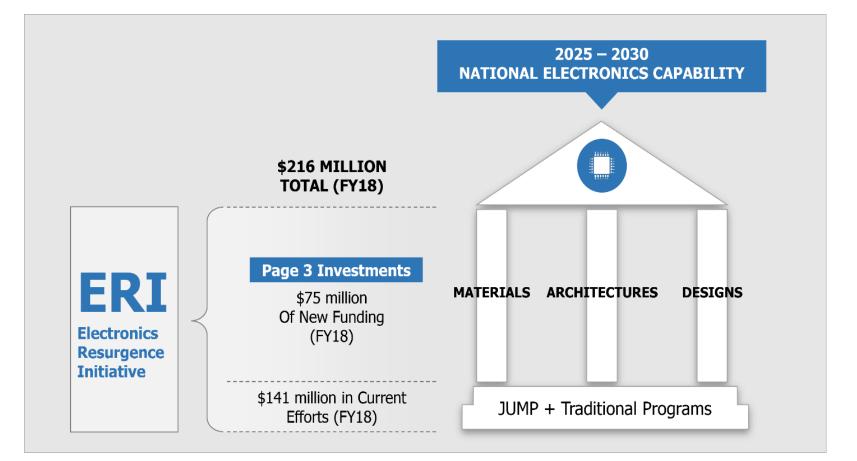

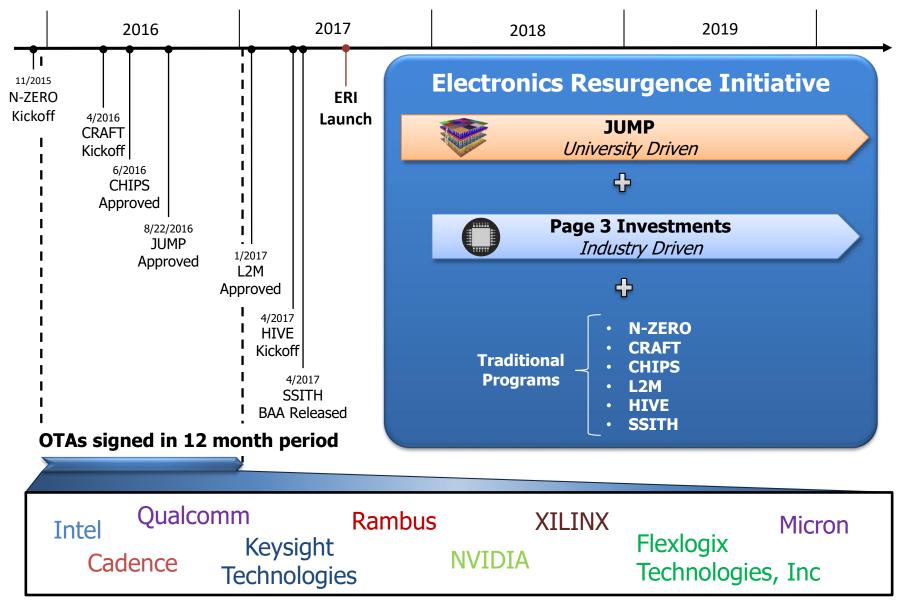

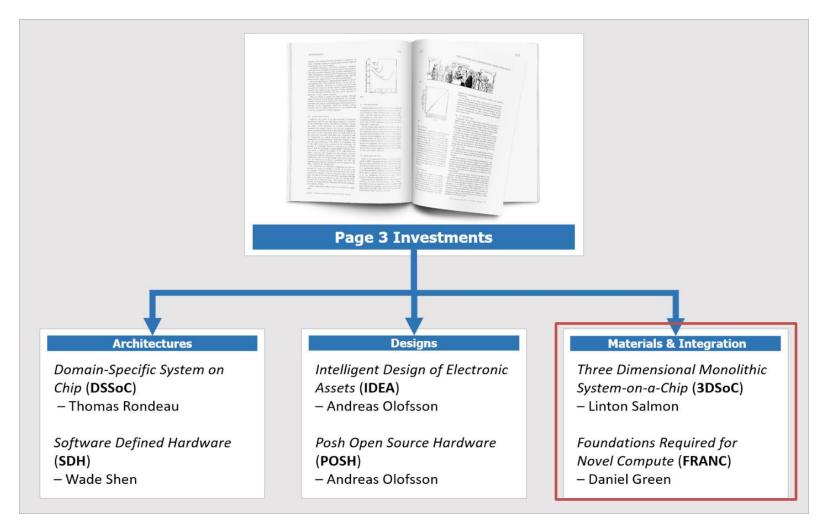

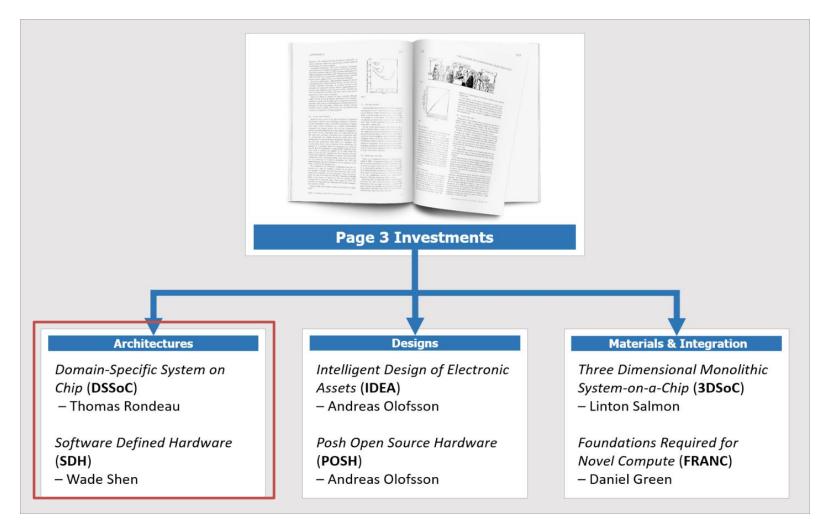

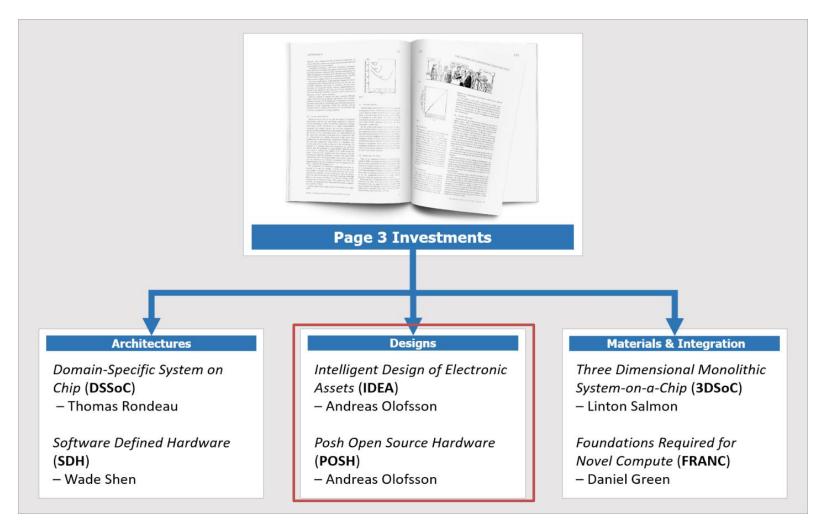

- ERI—creating an electronics capability that will provide a foundational contribution to national security

- Three thrust areas: Materials and Integration, Architectures, Designs

### VIII. DAY OF RECKONING

Clearly, we will be able to build such component-crammed equipment. Next, we ask under what circumstances we should do it. The total cost of making a particular system function must be minimized. To do so, we could amortize the engineering over several identical items, or evolve flexible techniques for the engineering of large functions so that no disproportionate expense need be borne by a particular array. Perhaps newly devised design automation procedures could translate from logic diagram to technological realization without any special engineering.

It may prove to be more economical to build large systems out of smaller functions, which are separately packaged and interconnected. The availability of large functions, combined with functional design and construction, should allow the manufacturer of large systems to design and construct a considerable variety of equipment both rapidly and economically.

# Materials & Integration

Adding separately packaged novel materials and using integration to provide specialized computing

# Recent DARPA investments and momentum

# Investments inspired by Moore's "Page 3"

Heterogeneous Integration directly part of Materials and Integration thrust and indirectly part of Architectures and Design thrusts as well

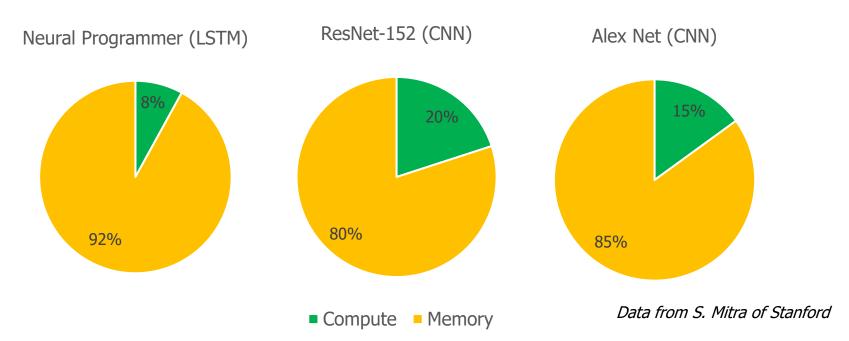

Current von Neumann architecture spends more time moving data than processing it

Data for 7nm instantiation of a state-of-the-art Machine Learning accelerator

# Accelerators don't help (enough) if using the same architecture

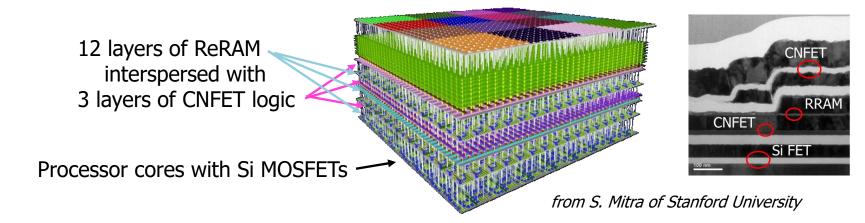

# An Integrated, Monolithic SoC (3DSoC) Solution

An example of an integrated flow that fabricates 3D logic and memory on a single die

Note: This is an example only. Other technical approaches are expected.

# **Critical characteristics for a monolithic solution**

- Must permit new architectures that leverage fast, configurable access to non-volatile main memory

- Stackable 3D logic and memory functions that allow new architectures

- Low temperature formation

- Logic AND memory

- High density of memory at least 4GB (Giga-Byte)/die

- Possible to fabricate in existing domestic, commercial, high-yielding infrastructure

- 90nm on 200mm wafers

- High yield on large SoCs

Source: S.F. Yitbarek, et al., DATE 2016.

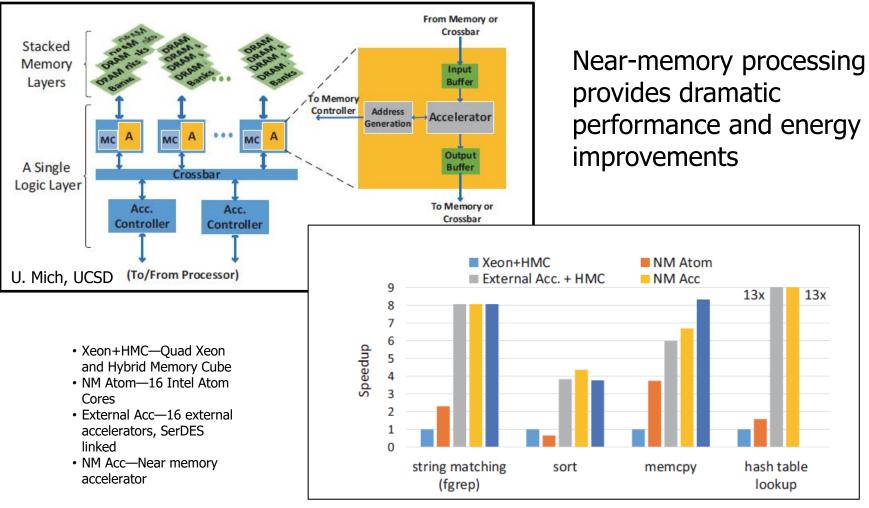

# FRANC leverages demonstrated benefits of beyond von Neumann topologies

Performance Comparison (higher better)

Key result: near-memory processing provides dramatic performance improvements

# Investments inspired by Moore's "Page 3"

Heterogeneous Integration directly part of Materials and Integration thrust and also indirectly part of Architectures and Design thrusts as well

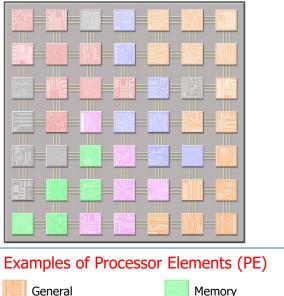

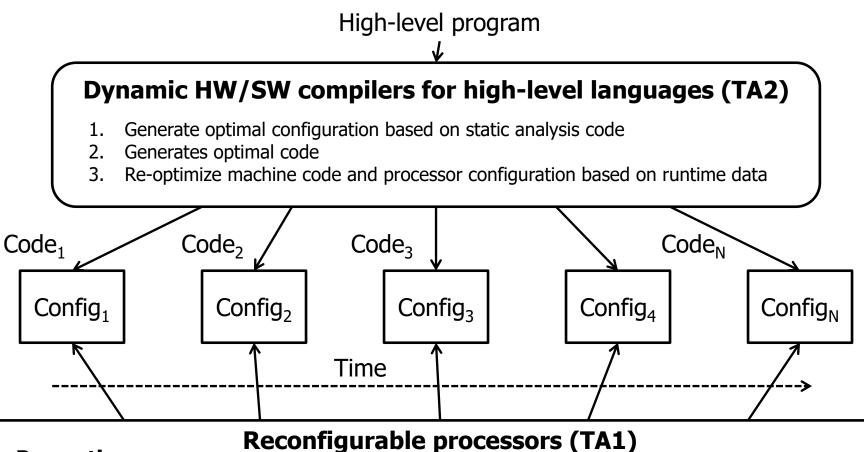

Build new processors that solve the significant computing needs of today's and tomorrow's applications.

Distribution Statement "A" (Approved for Public Release, Distribution Unlimited)

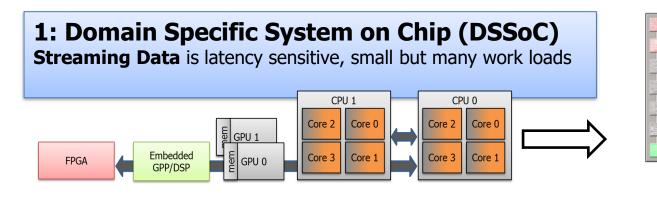

DSSoC

- Create a development ecosystem that takes advantage of the specialized hardware with no added burden to the programmer

- Design an intelligent scheduler for efficient data movement between DSSoC processor elements

- Build a DSSoC of advanced, heterogeneous processors and accelerators for software radio

DSSoC will enable rapid development of multi-application systems through a single programmable device

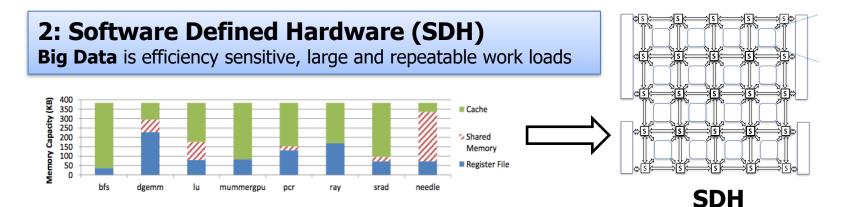

### **Properties:**

- Reconfiguration times: 300 1,000 ns

- 2. Re-allocatable compute resources i.e. ALUs for address computation or math

- 3. Re-allocatable memory resources i.e. cache/register configuration to match data

- 4. Malleable external memory access i.e. reconfigurable memory controller

# Investments inspired by Moore's "Page 3"

Heterogeneous Integration directly part of Materials and Integration thrust and also indirectly part of Architectures and Design thrusts as well

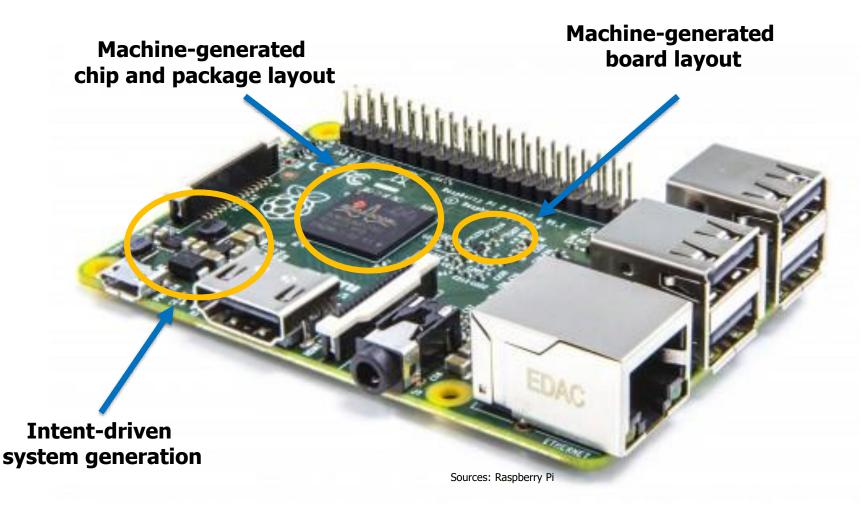

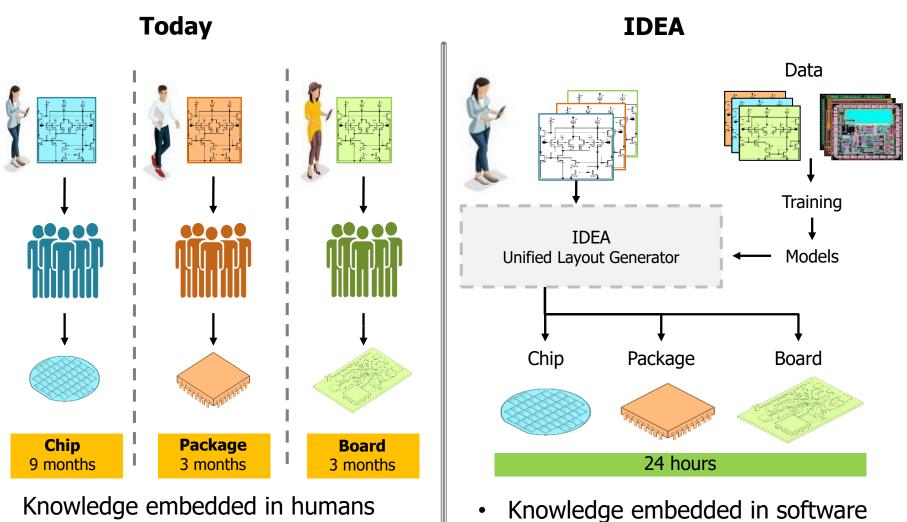

IDEA will completely automate the layout of electrical circuits and systems

# A unified electrical circuit layout generator

- Limited knowledge reuse

- Reliance on scarce resources

- 100% automation

- 24 hour turnaround

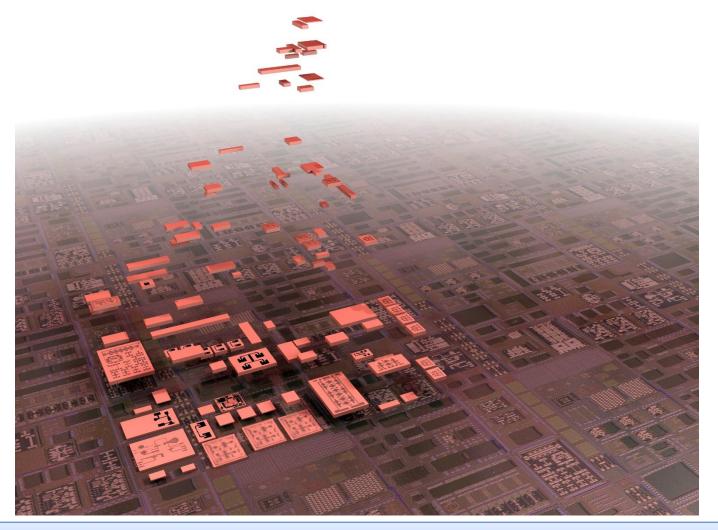

# **DARPA** Future of heterogeneous integration

# Requires a lot of pieces coming together!

Source: DARPA

www.darpa.mil