### **Electronic Interconnect Convergence**

... through large panel fan-out

**Tim Olson**

**Founder & CTO**

### Remember when? ... there were 3 distinct industries

#### Wafer Foundries

**Semiconductor Device**

**Nanometers**

**OSATs**

Packaging

10's of Microns

**EMS**

Electronic Systems

100's of Microns

### Remember when? ... there were 3 distinct industries

#### Wafer Foundries

**Semiconductor Device**

**Nanometers**

**OSATs**

**Packaging**

10's of Microns

**EMS**

**Electronic Systems**

100's of Microns

## Today, the lines are blurring

IEEE 67<sup>th</sup> ECTC -Orlando, FL, USA May 30 - June 2, 2017

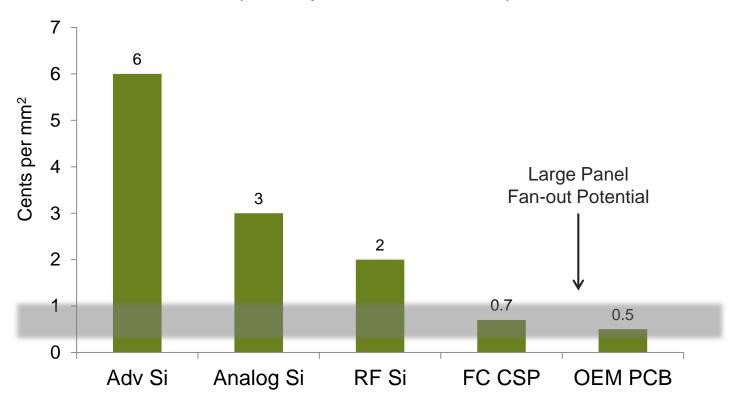

#### ... while electronic interconnect cost remains quite different

#### **Device Level Electronic Interconnect**

| <u>Technology</u><br>Digital processor | Typical Geometries  14 nm | Typical Cost 6 ¢ per mm² |

|----------------------------------------|---------------------------|--------------------------|

|                                        |                           |                          |

| RF                                     | 55 to 180nm               | 2¢ per mm²               |

Packaging - 1st Level Elec. Interconnect Typical Cost

Flip chip CSP packaging 0.7 ¢ per mm<sup>2</sup>

EMS - 2<sup>nd</sup> Level Elec. Interconnect

10 layer Smartphone motherboard 0.5 ¢ per mm<sup>2</sup>

Typical Cost

### Where does large panel fan-out fit?

# Technology Cost Comparison (Sales price to customers)

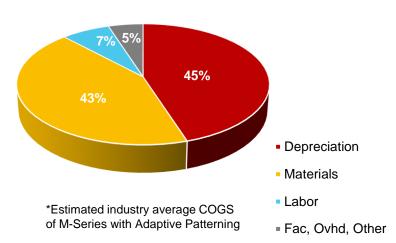

### The basics of cost for capacity

#### Wafer Processing Cost 300mm round baseline\*

Large panel fan-out has the potential for >30% cost reduction

- Capital productivity

- Material efficiency

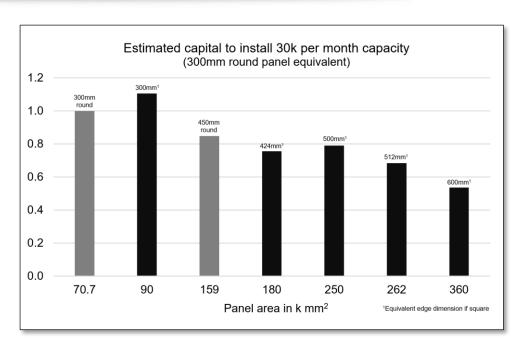

### **Breaking through the barriers**

Wafer level capital cost breakthrough

Solar wafer fab inspired approach

Chip attach cost breakthrough

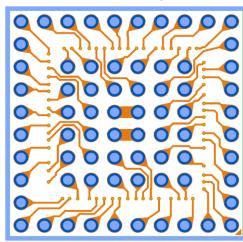

Adaptive Alignment\*

Align the entire RDL pattern to the measured die position

Enables high metal density designs Precisely aligns inductors to the die

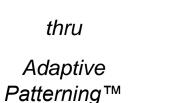

#### Adaptive Routing\*

Dynamically adapt RDL routing to the measured die position

BGA array fixed to package outline Enables multi-die fan-out

\*Note: Multiple patents issued & pending

#### ... the future is near

#### ... in cooperation with ASE

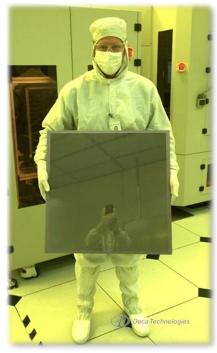

#### **Initial Production**

300mm round

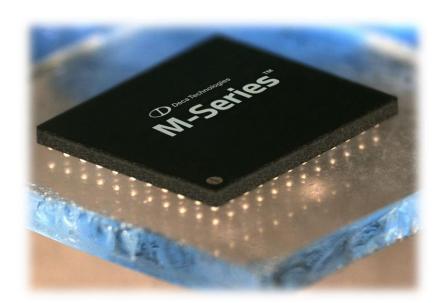

M-Series Structure\*

#### **Future Production**

(post chip attach)

(post mold & debond)

Large panel format M-Series\*

\*Note: Multiple patents issued & pending

## **Thank You**