# ALL PROGRAMMABLE

High Performance Memory in FPGAs

### **Industry Trends and Customer Challenges**

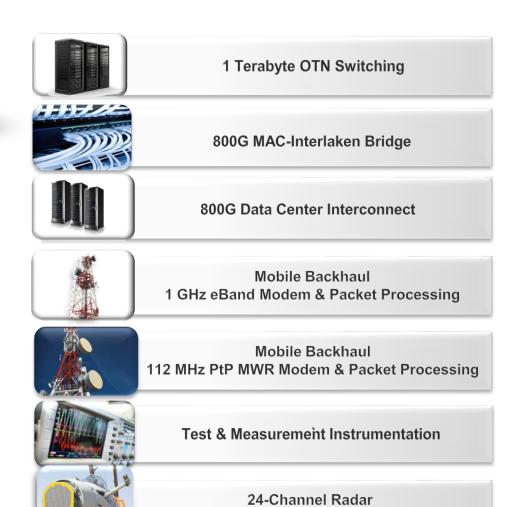

- > 400G OTN

- Software Defined Networks

- Video Over IP

Network Function Virtualization

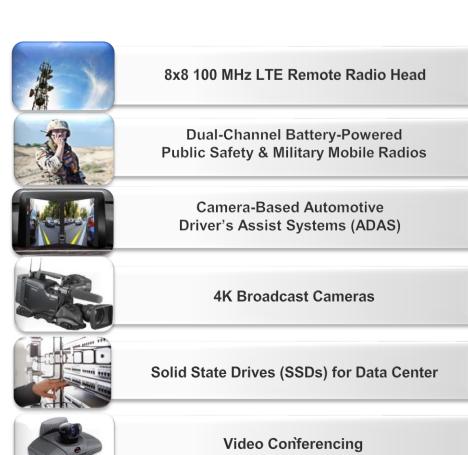

#### Wireless

- LTE Advanced

- Early 5G

Cloud-RAN

Heterogeneous Wireless Networks

#### Video and Vision

- 8K/4K Resolution

- Augmented Reality

- Immersive Display

- Video Analytics

#### Cloud and Data Center

- Acceleration

- Software Defined Data Center

Big Data

■ Public and Private Cloud

#### Industrial IoT

Sensory Fusion

- Machine to Machine Industry 4.0

- Cyber-Physical

- Embedded Vision

1

Performance & Power Scalability

2

System Integration & Intelligence

3

Security, Safety & Reliability

#### **FPGA** as System Enabler

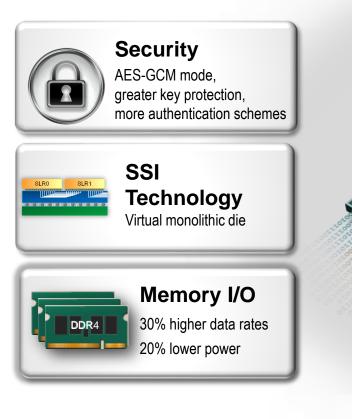

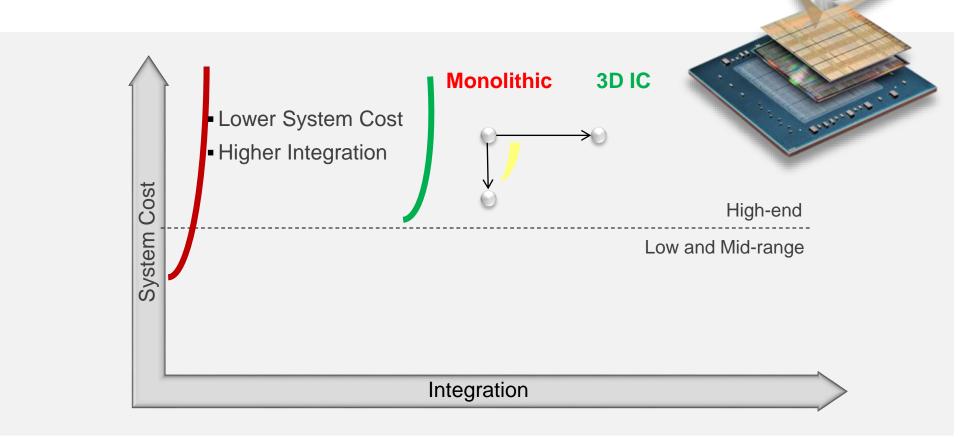

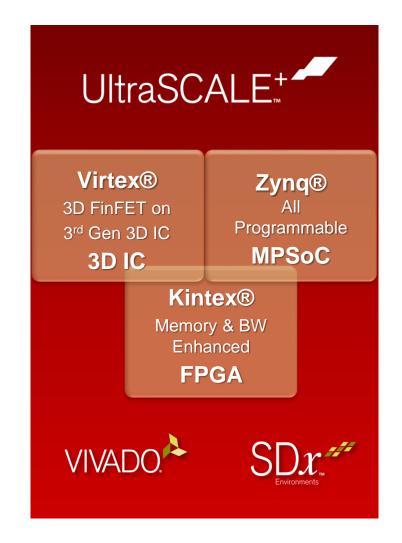

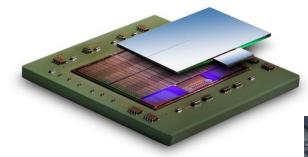

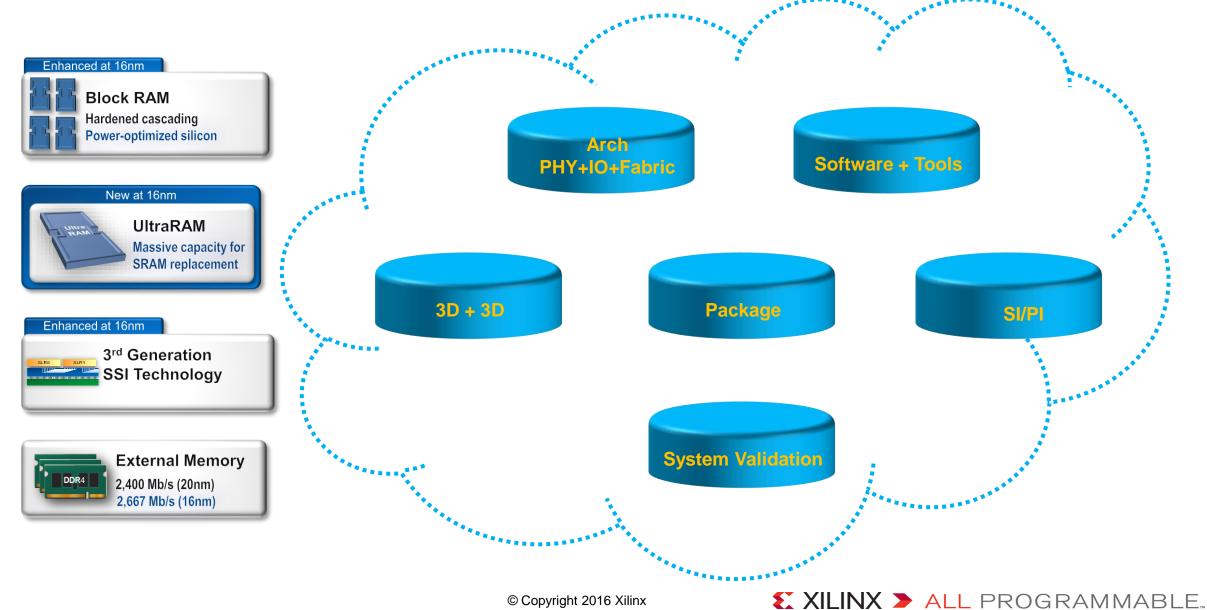

### **3D-on-3D: Another Industry First**

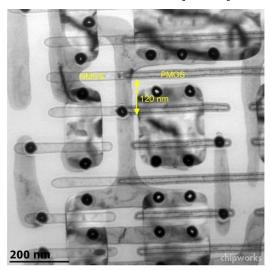

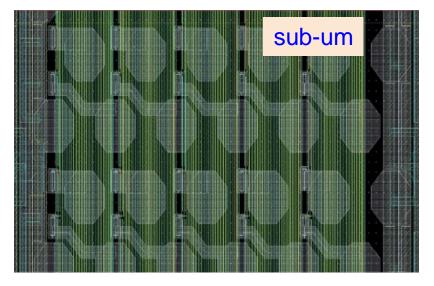

- > First 3D Transistors on 3<sup>rd</sup> Generation 3D ICs

- ➤ 3D Transistors: Non-linear improvement in performance/watt over planar transistors

- ➤ 3D IC: Non-linear improvements in integration & bandwidth/watt over monolithic ICs

# ASIC/CPU ←→ MPSoC

|                         | ASIC/CPU                                   | MPSoC                                                                              |  |  |  |

|-------------------------|--------------------------------------------|------------------------------------------------------------------------------------|--|--|--|

| I/O                     | 6x 2400 Mbps DDR4 (Xeon Phi)               | 5x 2667 Mbps DDR4 OR<br>9x 2400 Mbps DDR4                                          |  |  |  |

| Serial Link             | 32 PCIe + 3 QPI (Xeon 7)<br>36 PCIe        | 104 32.75Gbps GTY Transceivers                                                     |  |  |  |

| Core Vector             | Known pipeline and worst case power vector | Dependent on customer design                                                       |  |  |  |

| Clocking                | Single trunk clock                         | Multiple trunk clocks;<br>Highly configurable clocking                             |  |  |  |

| Package<br>Supply Rails | Mostly < 10                                | > 10                                                                               |  |  |  |

| Features                | Limited features for specific applications | Packed with features to cover variable customer needs (DSP, Networking IP and etc) |  |  |  |

| Software                | N/A                                        | Programmable Circuit                                                               |  |  |  |

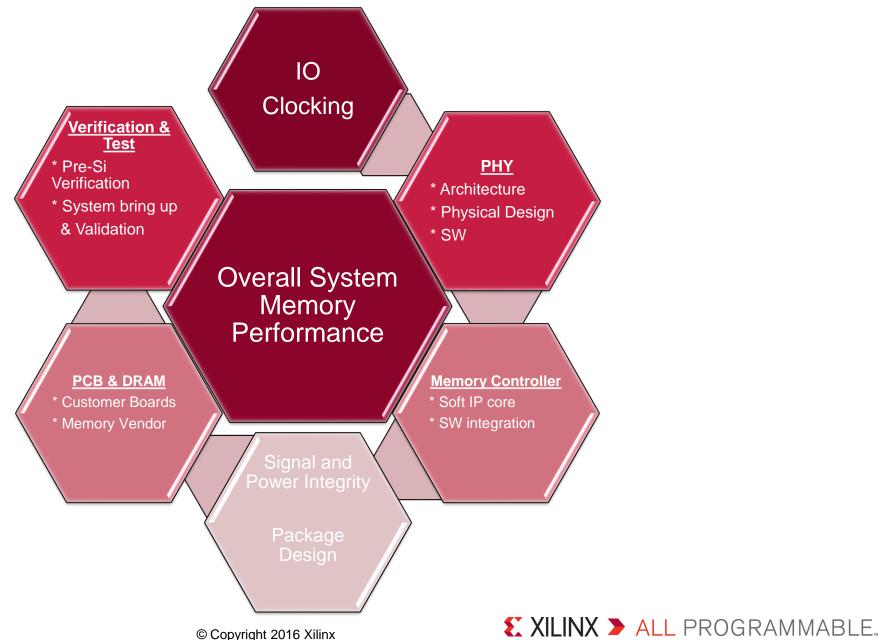

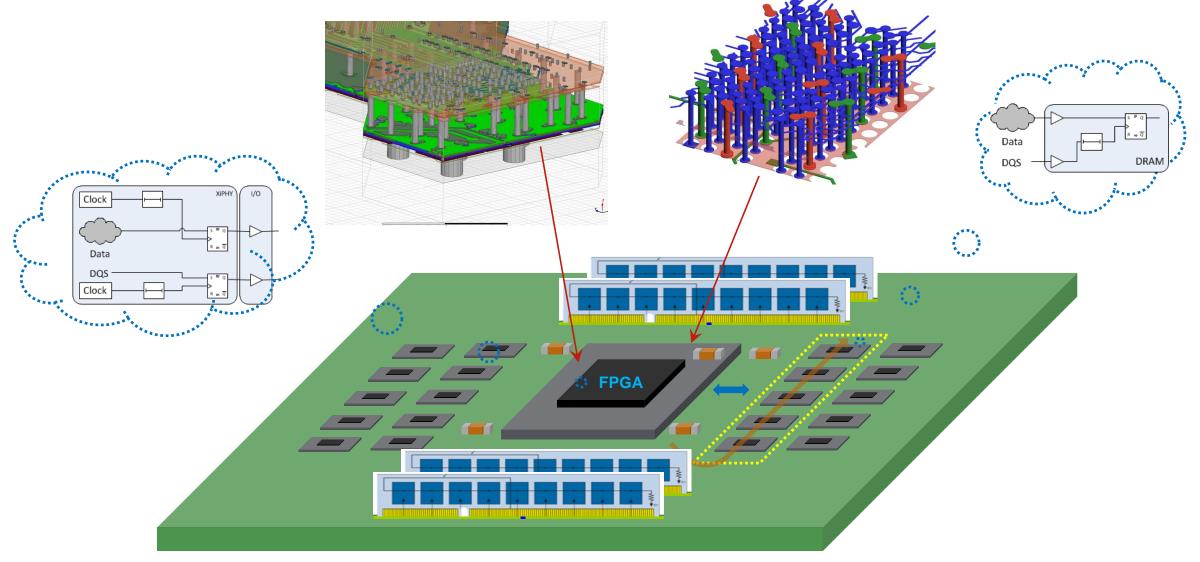

#### **FPGA Memory System Overview**

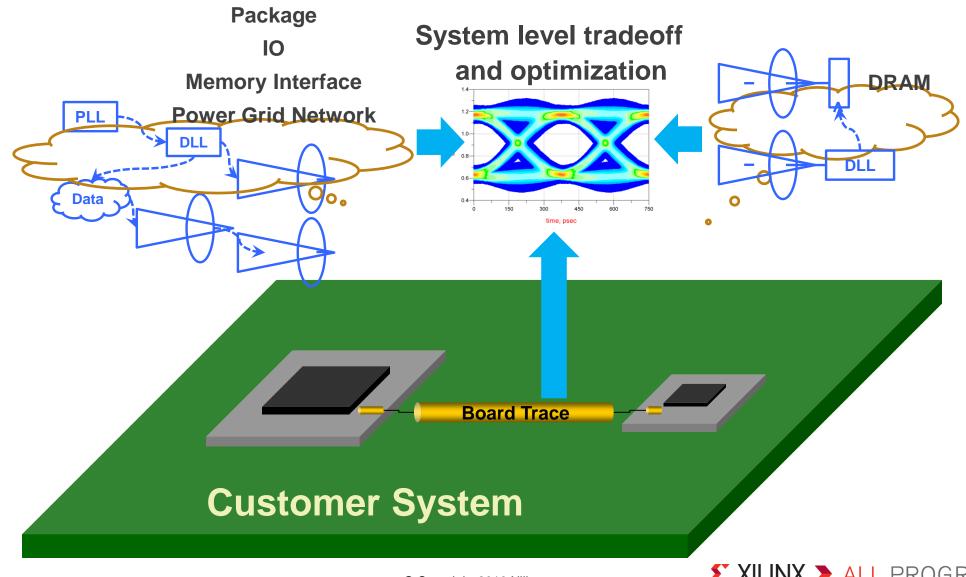

#### Memory is a **System Level** Optimization Challenge

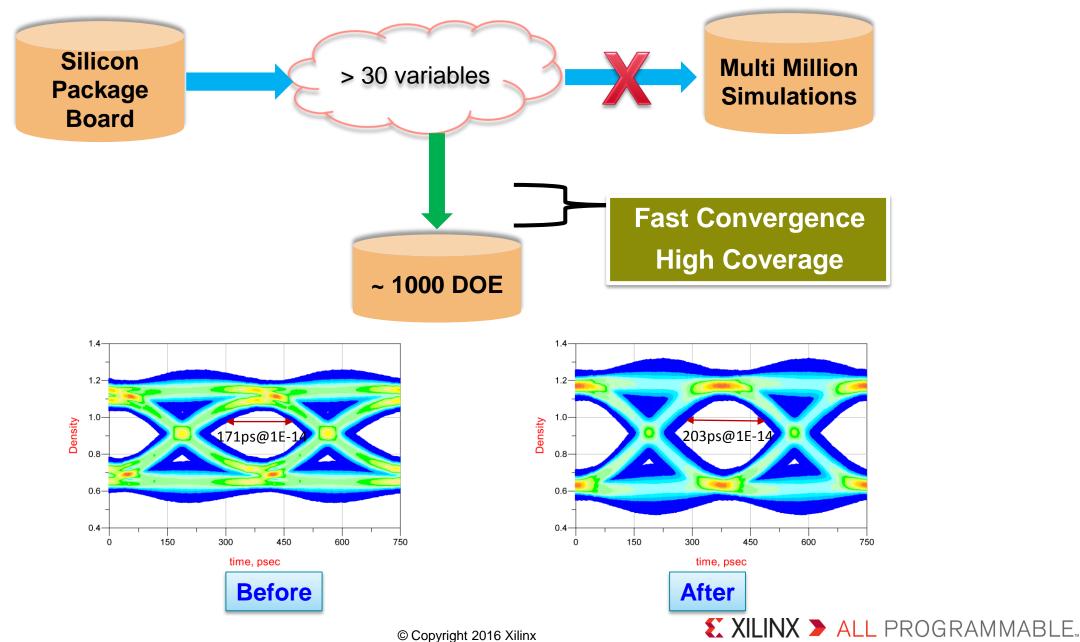

### **Critical Path DOE Optimization/Simulation**

#### **Packaging**

#### A Headache or Opportunity for Innovation and Product Differentiation?

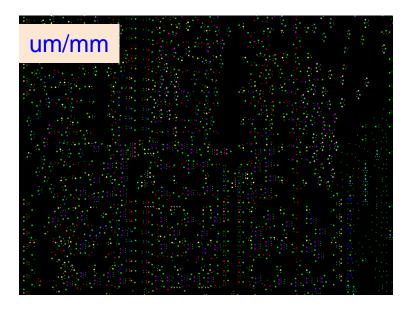

#### Nanometer to Meter and kHz to 33 Gbps

**Transistor (nm)**

**Board (meter/inch)**

Package (mm)

Memory

**VR Component**

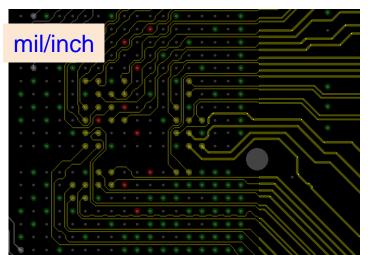

# **Physical Layout/Stack-up Example**

| Layer    | Туре    | CU<br>Weight | CU%  | Material Description    | Via Structure | Segment         | Glass Style         | Material Family | Dielectric<br>constant<br>@ 1GHz |

|----------|---------|--------------|------|-------------------------|---------------|-----------------|---------------------|-----------------|----------------------------------|

| Solderma |         |              |      |                         | 1.1           |                 |                     |                 |                                  |

| 1        | Mixed   | Т            | 6    | Press thk = 3.08 mil    |               | Foil<br>Prepreg | 1080(66)            | 370HR           | 3,90                             |

| 2        | Plane   | 1            | 98   |                         |               |                 |                     |                 |                                  |

| 3        | Signal  | 1            | 21   | 5.0 mil 1/1             |               | Core            | 1-1652              | 370HR           | 4.34                             |

|          |         |              | -    | Press thk = 4.43 mil    |               | Prepreg         | 106(75)             | 370HR           | 3.75                             |

| 4        | Plane   |              | 98   |                         |               |                 | 1080(66)            | 370HR           | 3.90                             |

| 4        | Plane   | 1            | 98   | 5.0 mil 1/1             |               | Core            | 1-1652              | 370HR           | 4.34                             |

| 5        | Signal  | 1            | 12   |                         |               |                 |                     |                 |                                  |

|          |         |              |      | Press thk = 4.32 mil    |               | Prepreg         | 106(75)<br>1080(66) | 370HR<br>370HR  | 3.75<br>3.90                     |

| 6        | Plane   | 1            | 98   |                         |               |                 | 1000(00)            | 37UHK           | 3,90                             |

|          |         |              |      | 5.0 mil 1/1             |               | Core            | 1-1652              | 370HR           | 4.34                             |

| 7        | Signal  | 1            | 10   | Press thk = 4.30 mil    |               | Prepreg         | 106(75)             | 370HR           | 3.75                             |

|          |         |              |      | F1655 BIK = 4.30 IIII   |               | Flepley         | 1080(66)            | 370HR           | 3.90                             |

| 8        | Plane   | 1            | 98   |                         |               |                 |                     |                 |                                  |

| 9        | Plane   | 1            | 98   | 3.0 mil 1/1             |               | Core            | 1-2113              | 370HR           | 4.28                             |

| 9        | Plane   | 1            | 98   | Press thk = 3.04 mil    |               | Prepreg         | 1080(66)            | 370HR           | 3.90                             |

| 10       | Plane   | 1            | 97   |                         |               |                 |                     |                 |                                  |

| 11       | Plane   | 1            | 98   | 3.0 mil 1/1             |               | Core            | 1-2113              | 370HR           | 4.28                             |

|          | 1 Idino |              | - 00 | Press thk = 3.04 mil    |               | Prepreg         | 1080(66)            | 370HR           | 3.90                             |

| 12       | Plane   | 1            | 97   |                         |               |                 |                     |                 |                                  |

| 13       | Plane   | 1            | 98   | 3.0 mil 1/1             |               | Core            | 1-2113              | 370HR           | 4.28                             |

| 13       | Filamo  |              | 00   | Press thk = 4.21 mil    |               | Prepreg         | 1080(66)            | 370HR           | 3.90                             |

|          |         |              |      |                         |               | //              | 106(75)             | 370HR           | 3.75                             |

| 14       | Signal  | 1            | 3    | 5.0 mil 1/1             |               | Core            | 1-1652              | 370HR           | 4.34                             |

| 15       | Plane   | 1            | 98   | 3.0 Hill 171            |               | Core            | 1-1032              | 37000           | 4.34                             |

|          |         |              |      | Press thk = 4.33 mil    |               | Prepreg         | 1080(66)            | 370HR           | 3.90                             |

| 16       | Signal  | 1            | 13   |                         |               |                 | 106(75)             | 370HR           | 3.75                             |

| 10       | olynai  |              | 13   | 5.0 mil 1/1             |               | Core            | 1-1652              | 370HR           | 4.34                             |

| 17       | Plane   | 1            | 98   |                         |               |                 |                     |                 |                                  |

|          |         |              | - 10 | Press thk = 4.21 mil    |               | Prepreg         | 1080(66)<br>106(75) | 370HR<br>370HR  | 3.90<br>3.75                     |

| 18       | Signal  | 1            | 3    |                         |               |                 | 100(75)             | STUPPE          | 3.75                             |

|          |         |              |      | 5.0 mil 1/1             |               | Core            | 1-1652              | 370HR           | 4.34                             |

| 19       | Plane   | _1_          | 98   | Press thk = 3.08 mil    |               | Prepreg         | 1080(66)            | 370HR           | 3.90                             |

| 20       | Mixed   | T .          | 4    | 1 1655 tilk = 3.06 IIII |               | Foil            | 1000(00)            | STUTIK          | 3.90                             |

| iderma   |         |              |      |                         |               | 7.00            |                     |                 |                                  |

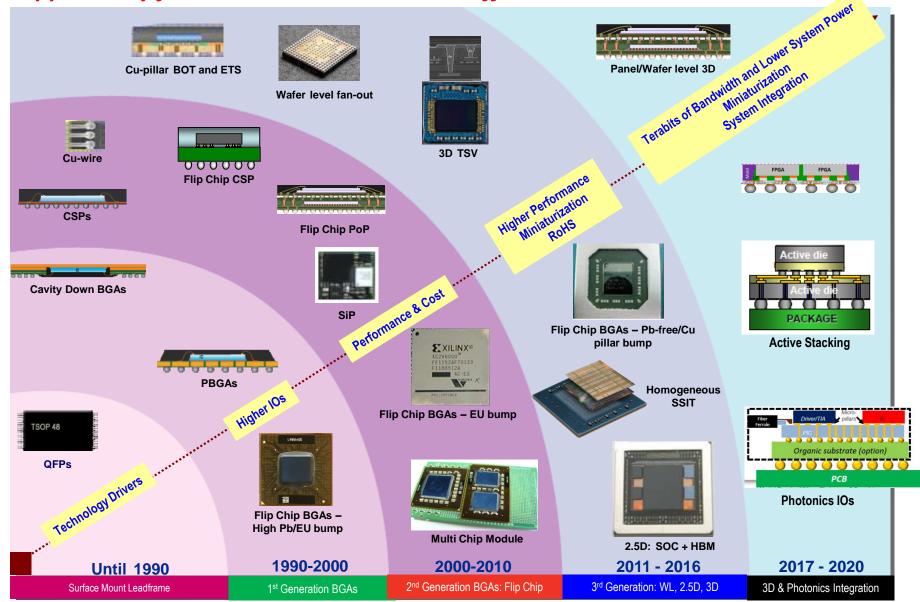

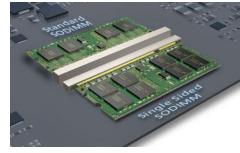

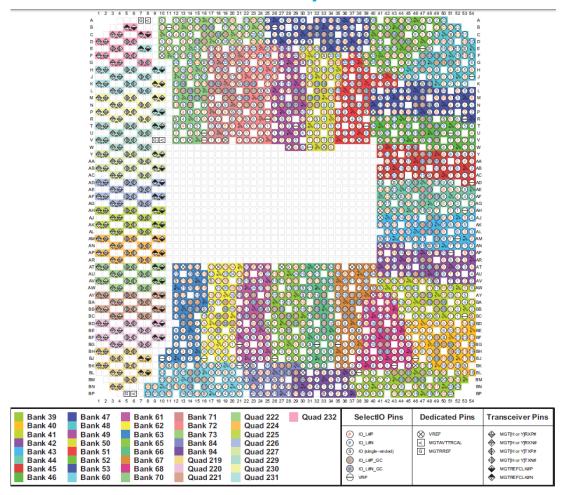

#### **FPGA Package Technology Impact**

#### 1404 HPIO pins

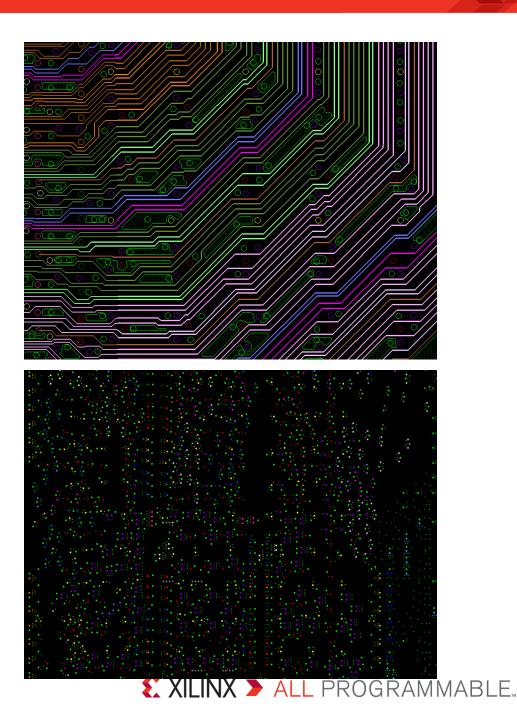

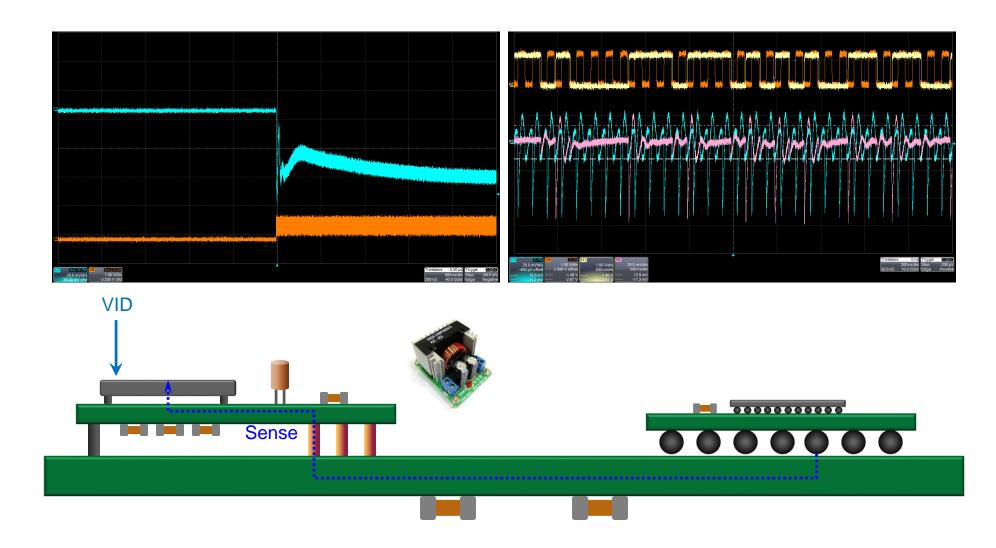

# **System Memory Channel Design**

### **Power Delivery System Overview**

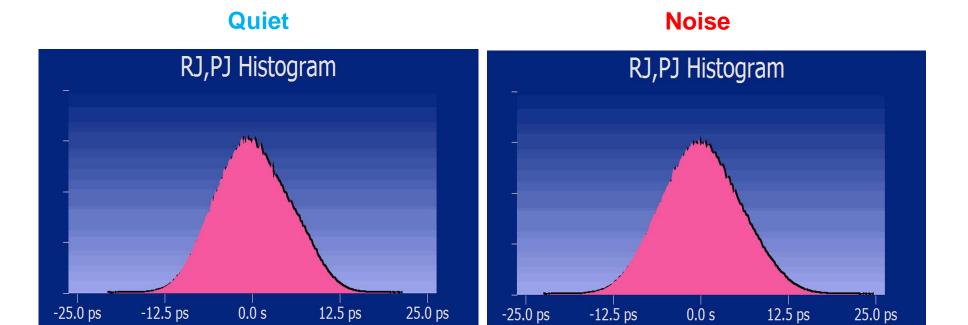

### **Power Delivery Result** → **Robust Timing Integrity**

**Timing Integrity**

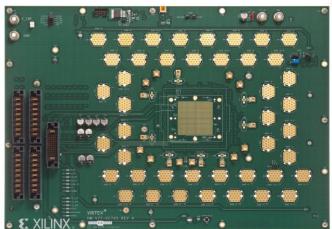

#### **FPGA Platform Memory Validation**

### **System Validation**

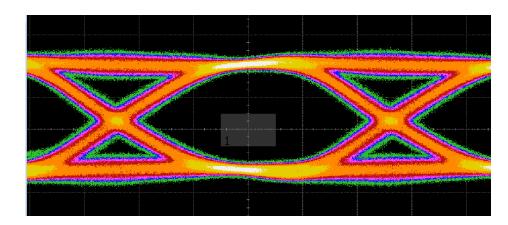

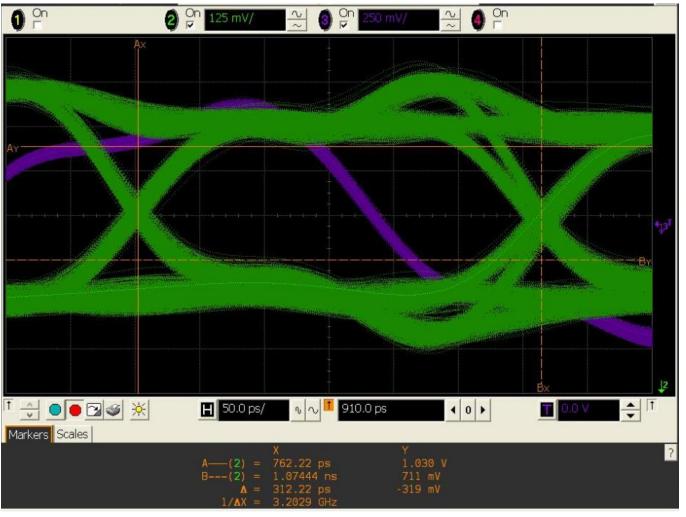

### DDR4 Memory Write Eye @ 3.2 Gbps

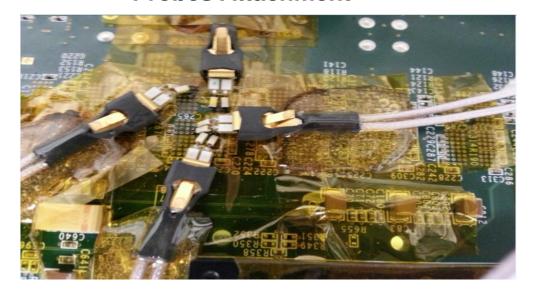

#### **Probes Attachment**

#### **Write Data Eye Capture**

#### **Challenges**

Power

Performance

Cost

System Validation

Package & Board Design

Application

Use cases

**High-Performance Scalable**

**Programmable Logic Controllers (PLCs)**

(Beamformer + Pulse Compressor + Doppler Filter)

Q & A