# LED Manufacturing: Could Silicon Displace Sapphire?

Aixtron

CRFF

YOLE DÉVELOPPEMENT

75 cours Emile Zola, F-69100 Lyon-Villeurbanne, France Tel: +33 472 83 01 80 – Fax: +33 472 83 01 83 Web: http://www.yole.fr

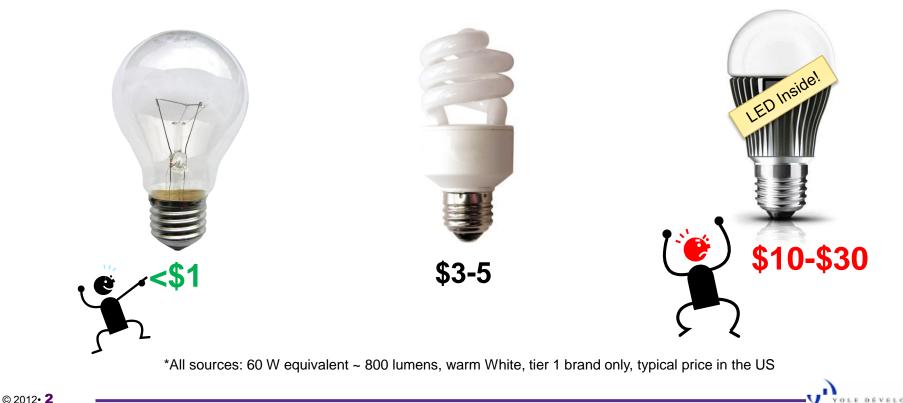

### LED Prices: where do we stand?

# LED price already "right" for some applications but need further improvements for others.

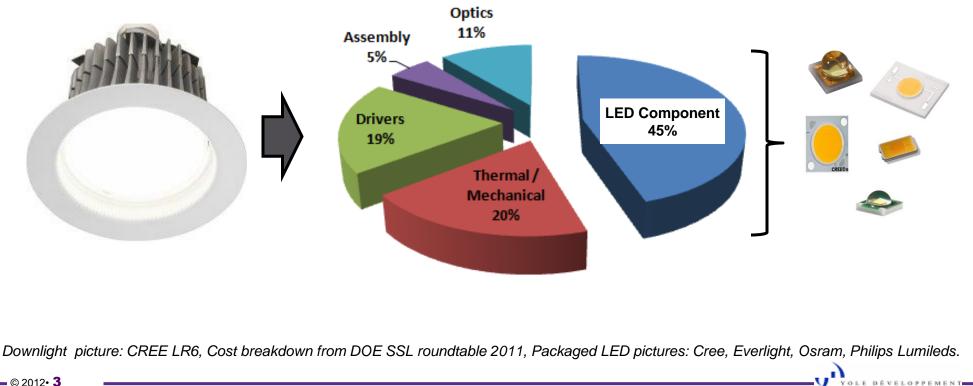

# **Luminaire Cost Structure**

# The packaged LED is only one contributor but represents the single largest BOM opportunity:

LED Downlight Luminaire <u>Cost</u> Breakdown

#### Copyrights © Yole Développement SA. All rights reserved.

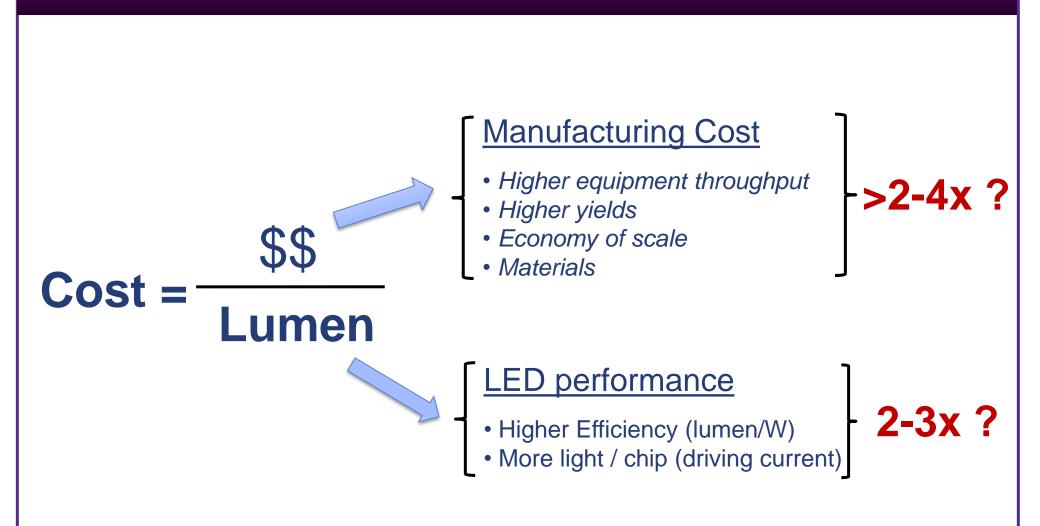

### **The Path to Cost Reduction**

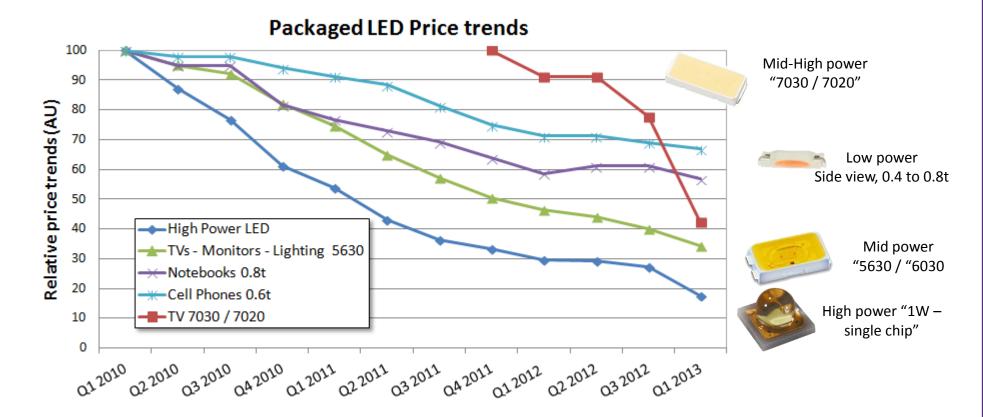

# 2010-2013 Trends

### Significant ASP drop with performance improvements...

# ...but more is needed for massive adoption in some applications

© 2012• 5

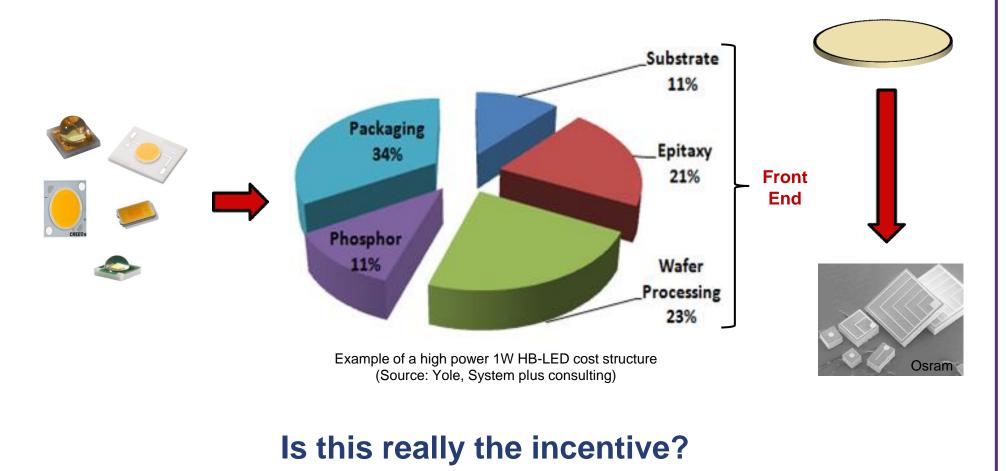

## **Packaged LED Cost Structure**

### Si wafers are less expensive than sapphire

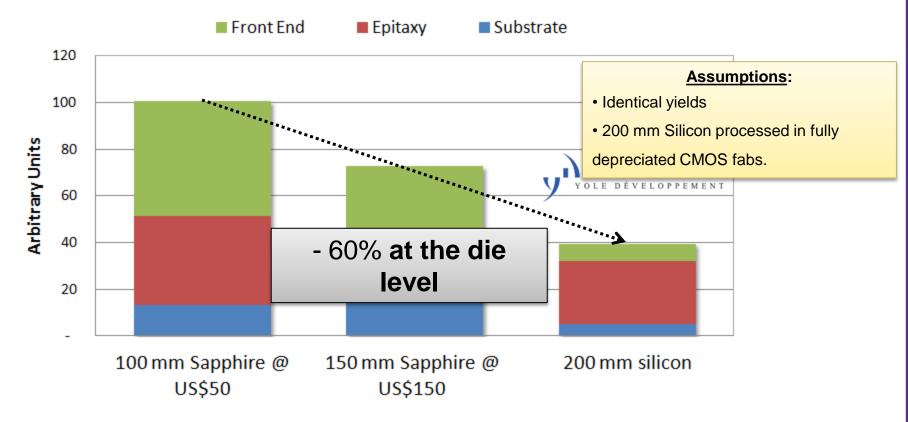

# **LED-on-Silicon: Potential Cost Benefits**

Epiwafer Manufacturing Cost per Unit Surface

Benefit of Si would stem from switching to 8" and using fully depreciated & highly automated CMOS fabs.

© 2012• **7**

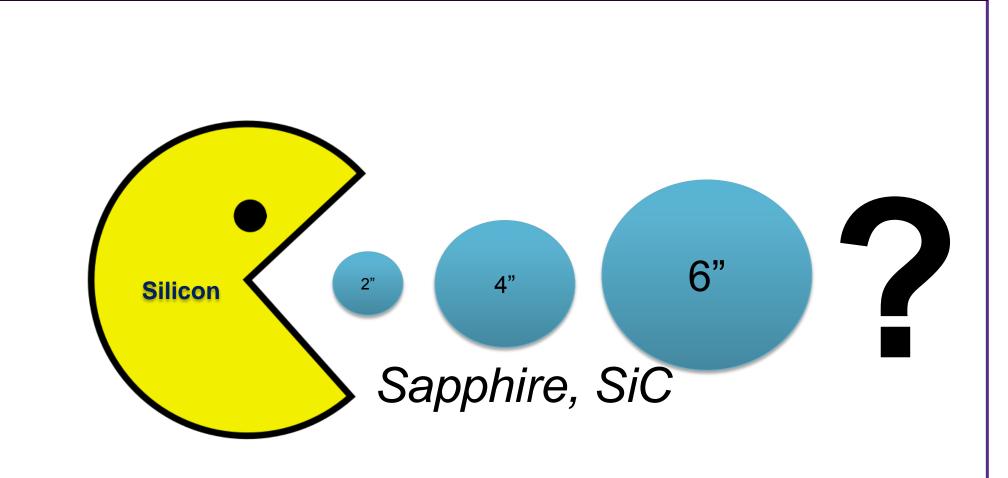

# Is Silicon Taking Over (yet)?

# **Potential Benefits:**

| CMOS processing                                                                                                    | Wafer Price                                                                                             | Higher Thermal<br>Conductivity       | Non Transparent<br>Material                            |

|--------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--------------------------------------|--------------------------------------------------------|

| <ul> <li>Mature, efficient<br/>(automated) &amp; high<br/>yield</li> <li>Large process<br/>toolbox</li> </ul>      | Silicon is cheaper<br>than sapphire and<br>will likely remain so.                                       | Better<br>Temperature<br>Homogeneity | More accurate<br>Surface<br>Temperature<br>Measurement |

| <ul> <li>Low cost: up to<br/>10x improvement<br/>vs. 2" sapphire (!?)</li> <li>New LED<br/>structures ?</li> </ul> | <ul> <li>Low wafer price</li> <li>200 mm available</li> <li>But not semi<br/>standard (yet?)</li> </ul> | Improved<br>Binning Yield ?          | Improved<br>Run/Run<br>repeatability ?                 |

### **Direct manufacturing cost**

#### **Potential yield benefits**

# Main Challenges:

|          | Lattice<br>Mismatch            | Thermal Expansion<br>Coefficient<br>Mismatch          | Melt Back    | Blue Light<br>Absorption by<br>Wafer |

|----------|--------------------------------|-------------------------------------------------------|--------------|--------------------------------------|

| Impact   | Epitaxial<br>Defect            | • Wafer Bow →<br>• In-homogeneity<br>• Layer Cracking | Poor epitaxy | Poor light<br>output                 |

| Sapphire | Bad                            | Bad                                                   | <u>No</u>    | <u>No</u>                            |

| Silicon  | Worse<br>P<br>Buffer<br>layers | Much worse<br>Much worse<br>Strain<br>Engineering     | Yes          | Yes                                  |

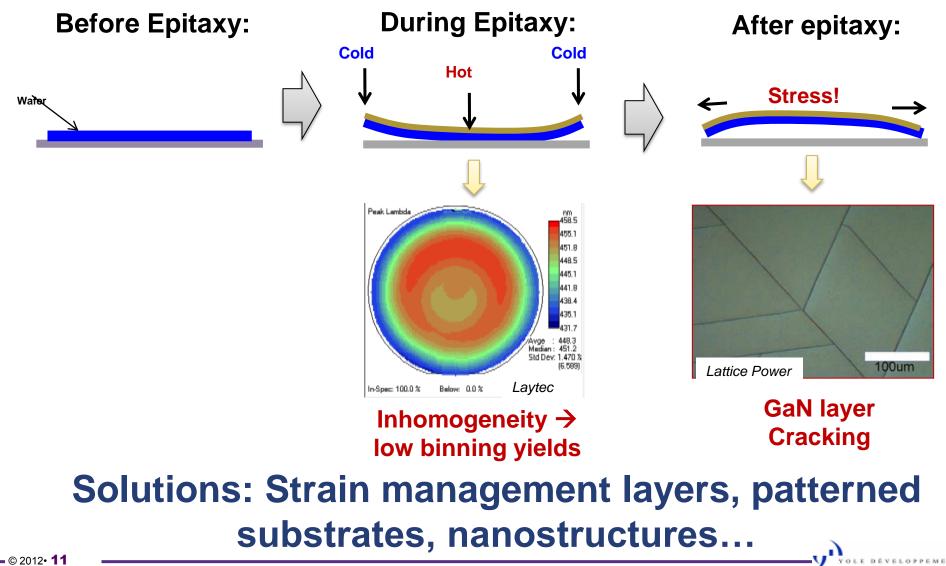

# Main Challenge: TEC Mismatch

Copyrights © Yole Développement SA. All rights reserved

# Main Challenges:

|              | Lattice<br>Mismatch | Thermal Expansion<br>Coefficient<br>Mismatch                      | Melt Back | Blue Light<br>Absorption<br>by Wafer |  |

|--------------|---------------------|-------------------------------------------------------------------|-----------|--------------------------------------|--|

| Impact       | Epitaxial<br>Defect | I • Wafer Bow →<br>• Inhomogeneity<br>• Layer Cracking Poor epita |           | Poor light<br>output                 |  |

| Sapphire     | Bad                 | Bad                                                               | No        | No                                   |  |

|              |                     |                                                                   |           |                                      |  |

| Silicon      | Worse               | Much worse                                                        | Yes       | Yes                                  |  |

|              |                     |                                                                   |           |                                      |  |

|              | Buffer              | Strain                                                            | AIN       | Substrate                            |  |

|              | layers              | Engineering                                                       | Buffer    | Lift Off                             |  |

| - © 2012• 12 |                     |                                                                   |           |                                      |  |

**©** 2012• **12** Copyrights © Yole Développement SA. All rights reserved.

### **Conditions for Success**

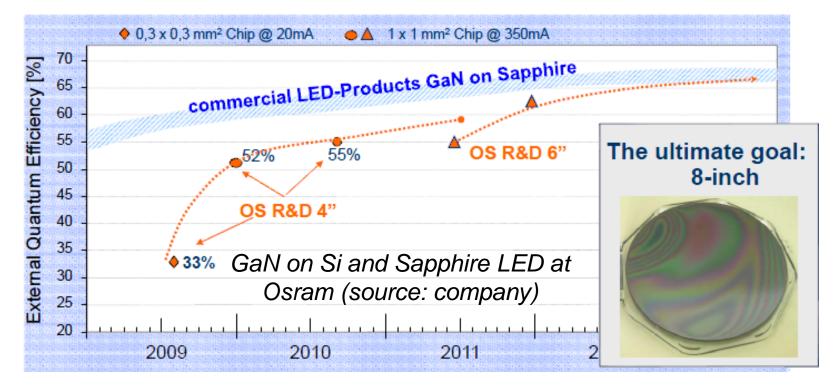

# #1: Must equal LED on Sapphire performance.

# **Performance Status: Example**

### Absolute LED on Si performance still behind sapphire state of the art but catching up (Bridgelux, Lattice Power, Osram...)

Performance: 634 mW @ 3.15 V, 350 mA, 1 mm2 chip → chip operated at 35 A/cm<sup>2</sup>, standard package

## **Conditions for Success**

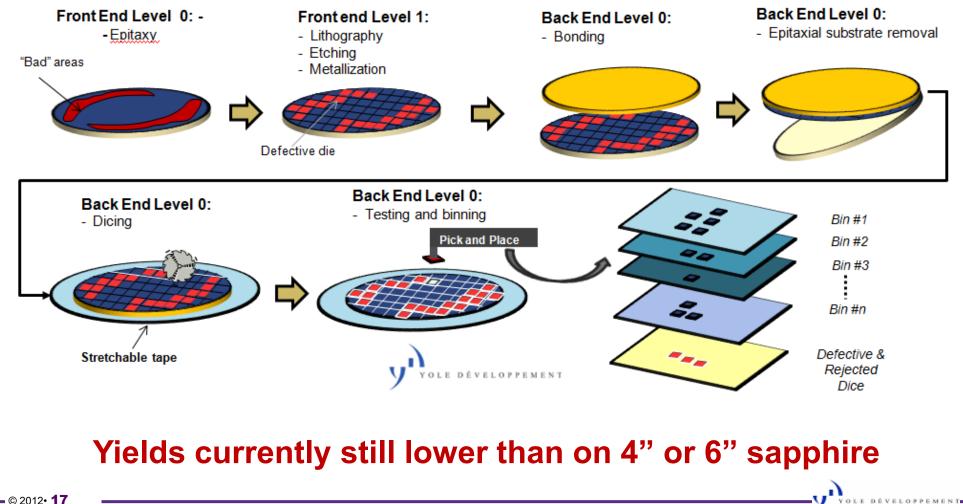

# #2: Must reach manufacturing yields similar to sapphire/SiC.

# Manufacturing & Binning Yields

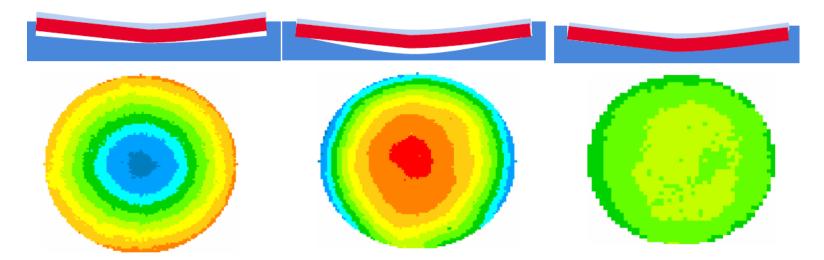

### Main Issue: Wafer bow during epitaxy. Getting worse with larger diameter!

Wafer mapping of the Photoluminescence of Multi Quantum Wells with wafers seating in pockets with different shapes. Source: Aixtron

# Solutions include thicker wafers, curved pockets: requires extremely stable and reproducible process

Copyrights © Yole Développement SA. All rights reserv

© 2012• **16**

# Are Yields Still important if Processing Since CMOS Processing is Cheaper?

### Yes: bad die carry the same cost as good ones!

## **Conditions for Success**

# #3: Must be compatible with CMOS, ideally on 200 mm wafers (China: 150 mm fabs also available)

# **Compatibility with CMOS Fabs**

|                                             | Diameter                                       | Epiwafer Bow                                      | Wafer<br>Thickness                 | Contamination                        | Wafer<br>Reflectivity                                        |

|---------------------------------------------|------------------------------------------------|---------------------------------------------------|------------------------------------|--------------------------------------|--------------------------------------------------------------|

|                                             | 6" mininum<br>≥8" better                       | < 50 – 60 um                                      | 725 um<br>(200 mm wafers)          | No gold                              | Reflective surface                                           |

| LED<br>on<br>Al <sub>2</sub> O <sub>3</sub> | Available but<br>(still)<br>expensive          | Can be managed<br>but need very<br>thicker wafers | 6": 1 to 1.3 mm<br>Not compatible! | Used for bonding<br>and other layers | Incompatible<br>with equipment<br>sensors and<br>automations |

| LED<br>on Si                                | Available and<br>cheap.<br>150, 200,<br>300 mm | OK with strain management layers.                 | > 725 um: can<br>be thinned down   | Used for bonding<br>and other layers | OK                                                           |

YOLE DÉVELOPPEMENT

# **Conditions for Success: Summary**

- Performance Must equal LED on Sapphire.

Coming close.

- Must reach yields similar to Sapphire/SiC

- Still far away and needing significant improvement

Must be CMOS compatible, 200 mm preferable

Still some efforts needed

## Incentive for LED-On-Si is COST not performance!

# **Players and Recent News**

#### • Most LED makers have LED on Si research programs:

- OSRAM

- Philips Lumileds

- Samsung

- Bridgelux + Toshiba

- Epistar

- Lattice Power

- TSMC...

Osram 6" LED Epiwafer

Bridgelux 8" LED Epiwafer

Lattice Power Led-On-Si chip

- Multiple startups (e.g.: Aledia...)

- Bridgelux/Toshiba, Lattice Power, Plessey committed to Si transition.

Samsung also has strong incentive (CMOS fabs available)

- Most still undecided or in "defensive mode"

- New LED industry business models?

- Azzurro offering GaN on Si templates or full LED epiwafers → fabless LED makers.

# **Players and Recent News**

### Mixed signals at TSMC and Epistar:

### TSMC:

- "it is difficult for 8-inch Si-substrate GaN wafers to replace sapphire wafers to become mainstream LED material because the former's manufacturing process is complicated and brightness of LED chips is lower" – Jacob Tam, President TSMC Solid State Lighting, January 2013.

- "It is understood that in the current stage, TSMC Solid State Lighting GaN-on-Silicon and sapphire substrate LED production line revenue is 50%, differentiated by using high-power and low-power LEDs" – Digitime April 2013.

#### **EPISTAR:**

- Epistar transferred its GaN LED structure to an Si with Azzurro templates in just 16 weeks.

While Epistar has not announced plans for production of GaN-on-Si LEDs PR Oct 2012

- Chairman Lee Biing-jye, indicated that yield rates for Si-substrate GaN wafers are still low and Epistar is developing production technology for breakthrough". - Digitime. Jan 2013

# **Players and Recent News**

### But others moving on:

#### Bridgelux (US)/ Toshiba (JP):

- December 2012: Toshiba says it is <u>shipping GaN-on-SI LEDs</u> but no evidence yet of products that use the LEDs have been verified on the market

- April 2013: Bridgelux sells silicon IP to Toshiba.

#### Plessey (UK)

- March 2013: Plessey announces shipment of GaN-on-Si LEDs using 6-in wafers but first products only offer flux output in the 1-3-lm range 15-36 lm/W at 3.3V / 25 mA)

- Target for next product release: 60-70 lm/W

#### **Lattice Power:**

- Feb 2013: volume production of high power chips but still on 2" Si wafers. Not much cost saving vs. sapphire but plan to switch to 6" soon.

- Currently run 15k to 20k wafers per month.

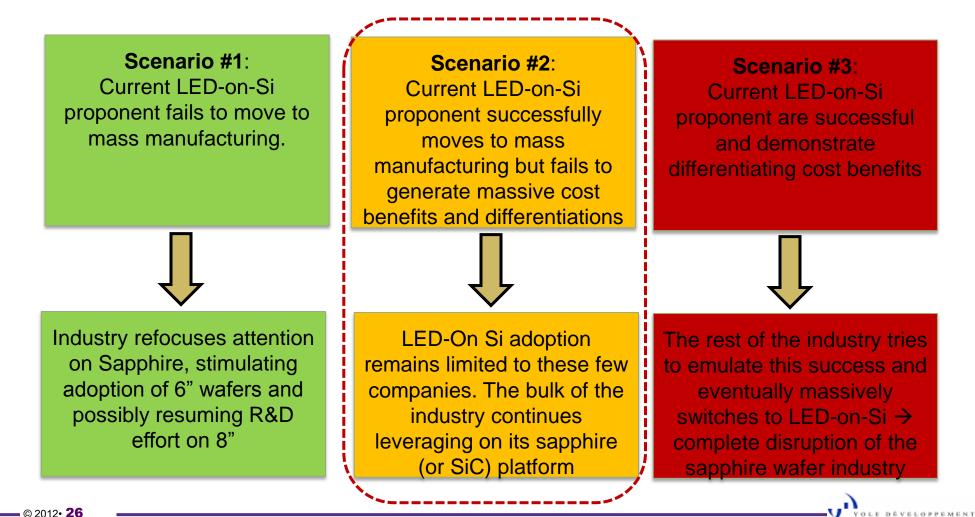

# Will LED-on-Si Happen?

- Still some technology hurdles: yields, full CMOS compatibility.

- LED on Si better suited for some type of LEDs than others and breakeven point not the same for all manufacturers.

Tier one LED Maker with advanced LED on sapphire technology and large installed capacity Large Semiconductor company with existing CMOS capacity willing to enter the LED Market Start-up or LED company willing to scale up capacity without massive CAPEX → "Fabless" model

Incentive

If technology hurdles are cleared, LED-On-Si will be adopted by <u>some</u> LED manufacturers but not necessarily become the standard.

# Will LED-on-Si Happen?

# Maybe...

- It's a cost game (\$/lumen)!

- Si enables 200 mm in CMOS fabs

- Sapphire/SiC = moving targets!

Copyrights © Yole Développement SA. All rights reserved

### **Our Scenario**

- <u>If</u> technology hurdles are cleared, LED-on-Si will be adopted by <u>some</u> LED maker, but not necessarily become the industry standard.

# THANK YOU! I YOOLE Développement

Contacts (US): Michael McLaughlin: mclaughlin@yole.fr 650-931-2552

> www.i-**micronews**.com www.yole.fr

Copyrights © Yole Développement SA. All rights reserved